# Merged Logic and Memory Fabrics for Accelerating Machine Learning Workloads

# Brian Crafton, Samuel Spetalnick, Yan Fang, and Arijit Raychowdhury

Georgia Institute of Technology

#### Editor's notes:

Designing hardware accelerators for machine learning (ML) applications is a well-researched problem. This article presents a tutorial regarding new computing architectures, circuits techniques, and multiple promising device technologies for in-memory computing targeting ML workloads.

-Partha Pratim Pande, Washington State University

**TODAY'S COMPUTING SYSTEMS** and emerging workloads are heavily dependent on the capacity and latency of memory banks, thanks to the increasing performance gap between main memory and logic. Decades of research and the majority of on-chip area in modern integrated circuits (ICs) has been dedicated to creating complex memory hierarchies to negate this growing performance gap. Although this design strategy works well for general-purpose computing, recent trends in data analytics and artificial intelligence have further exacerbated the long-standing memory bottleneck. Rather than fast single threaded performance and unknown data-access patterns, these applications require massively parallel computation and fixed, known data-access patterns. As a result, the clever caching hierarchy that takes advantage of spatial and temporal data reuse is overwhelmed by the vast amount of data required

Digital Object Identifier 10.1109/MDAT.2020.3016587 Date of publication: 14 August 2020; date of current version: 10 March 2021. by new applications. Because these elaborate caching schemes have been rendered practically useless owing to the embarrassingly parallel nature of emerging applications, traditional

processors have failed to provide either the performance or energy-efficiency that are demanded by these workloads.

Consequently, we have seen a plethora of high-quality software packages, such as TensorFlow [1] and PyTorch [2], and hardware packages, such as Google's tensor processing unit (TPU) [3] and Nvidia's Volta, that vastly outperform previous top of the line commercial general-purpose hardware. Unfortunately, it is inevitable that these improvements will again slow down and the hardware solutions will be limited in performance by the memory bottleneck. To make matters worse, the cost of moving data has become more expensive than operating on it [4], [5]. So not only has memory become the fundamental bottleneck of computing, but both reading and transporting the data throughout the growing size of modern ICs has become more expensive than the operation we seek to perform.

This has given rise to various areas of research to mitigate the memory bottleneck, and tremendous effort is being driven from the device to the architectural levels. At the top of the computing hierarchy,

**January/February 2021**

Copublished by the IEEE CEDA, IEEE CASS, IEEE SSCS, and TTTC

39

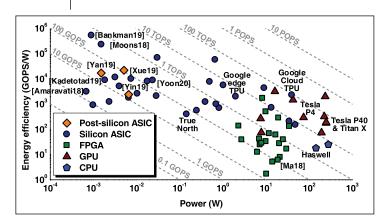

Figure 1. Recent advances in machine learning hardware spans over a large power-performance design space. (Source: Dr. Jong-Hyeok Yoon, Georgia Tech.)

computer architects and compiler designers are attempting to use the same CMOS technology, but use advanced dataflow patterns and mapping strategies so that the data movement is minimized and data reuse is maximized. Several recent demonstrations in

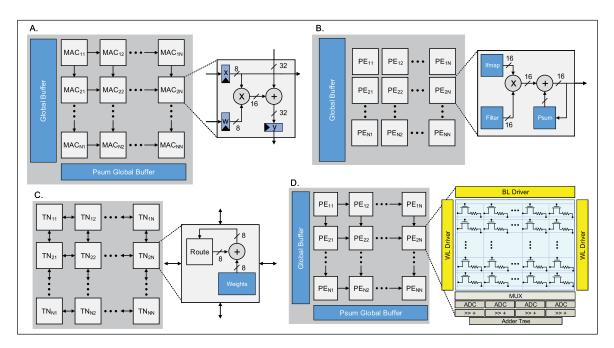

machine learning hardware have made tremendous advances in both performance and energy-efficiency, and this is illustrated in Figure 1. Original works [6], [7], created accelerators to match the architectures of emerging deep neural networks (DNNs). Later works [5], [8], [9] showed the primary opportunity for improving the performance of these accelerators is maximizing data reuse (or minimizing total data transport). The initial demonstration of this technique was Everiss [5] in 2016, but since then new strategies for both reinforcement learning (RL) [10] and recurrent neural networks (RNNs) [11] have also been demonstrated in silicon. Furthermore designs using mixed signal compute [12], [13] have also been demonstrated using low and variable precision. Although these designs feature data reuse and reduced power, they make application specific design choices which reduce their generality in a wide spectrum of applications. In Figure 2a and b, we show architectural differences between the TPU [3] and Eyeriss [5]. By placing small caches inside of the processing elements (PEs), Eyeriss is able to reuse feature maps and filter weights

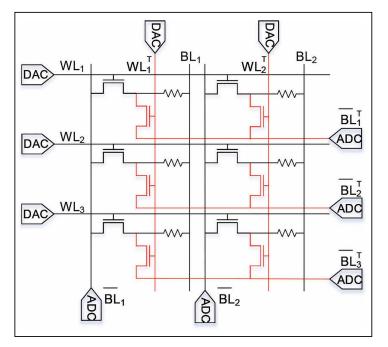

Figure 2. Four architectures used by machine learning accelerators. The memory used to store weights and input data is colored in blue. (a) Systolic array used by the TPU [3]. (b) Systolic array with local cache for filters and feature maps to maximize data reuse used by Chen et al. [5]. (c) SNN architecture with all weights stored local to neuro-synaptic core used by Merolla et al. [19] and Davies et al. [20]. Each core stores weights for many neurons, computing is shared among all neurons mapped to the core. (d) In-memory architecture using RRAM. Computing and memory are combined so there is no memory transfer. Analog-to-digital converters (ADCs) are still shared among inputs and outputs to the array.

rather than reading and transporting them for each output neuron. More recent works [14]–[17] are attempting to exploit sparsity and compression in both weights and activations of large networks. This is particularly important in emerging models for natural language processing [18] where huge numbers of parameters are used.

In a radically different approach spiking neural network (SNN) chips like [19] and [20] attempt to only read and modify weights using their respective neuron. As a result, large amounts of static random access memory (SRAM) and low precision weights are required to keep all weights on chip without having to fetch them from the main memory. This is demonstrated in Figure 2c, where no global buffer is used and the only transfer of data is directly between cores. Because weights are only accessed by a single core, compute units are not reused across the various layers. This is not ideal from a performance perspective because it means latency will be much higher given that only a fraction of the compute units are used for a given layer. The throughput can potentially be recovered if all the layers are pipe-lined. However, the biggest advantage of this dataflow architecture is its ability to reduce global movement of data. This design strategy is commonly referred to as near memory computing, where the objective is to physically place compute and memory together rather than keep them separated by a high performance memory controller. While this is a useful technique and we can expect significant power savings, it will still face some of the fundamental technological limitations of CMOS.

It is critical to understand the role of embedded nonvolatile memory (eNVM) on future computing platforms. Volatile memory solutions for on-die integration are typically charge-based: SRAM and embedded-DRAM (eDRAM). Both these technologies consume zero standby power-in terms of leakage (SRAM) or refresh (eDRAM) power. With the growing need for larger and larger on-die memory for machine learning applications, the total standby power continues to be a significant limitation in the energy efficiency of SRAM- and eDRAM-based systems. Hence, eNVM is expected to alleviate this challenge. Furthermore, the eNVM solutions that are currently being pursued include noncharge-based physical states-such as ion movement or spin polarization. These physical phenomenon are often scalable to dimensions that are smaller than what SRAM or eDRAM can enable. Consequently, eNVM technologies continue to gain popularity as both a research vehicle as well as a solution at the end of the scaling roadmap.

Fortunately, for more than a decade there has been a steady increasing effort in design, fabrication, and manufacturing of novel memory technologies that are logic process and voltage compatible, while providing high density as well as target read and write performance. These new devices have exciting new properties that have been long absent in traditional charge based memory technologies. The four such technologies that we discuss in this article share the following properties [21]:

- They are all eNVM solutions. They can be completely powered down without loss of data, and hence consume virtually no leakage power.

- All these technologies are process and (somewhat) voltage compatible with CMOS logic processes, although more advances need to be made on both fronts.

- All these technologies store information through change of resistance. This enables us to perform compute in-memory (CIM) on the bitline (BL) with breakthrough improvements in throughput and energy-efficiency.

These properties have the potential to realize the long awaited benefits of in-memory computing. In addition to these properties, new eNVM technologies feature high density and often multilevel cells (MLCs) where more than a single bit can be stored per cell. In comparison, modern 6T SRAM can be as large as  $150F^2$ while only offering a single bit of differential storage. In-memory computing uses physical properties of the devices to do computation without a dedicated compute unit. Using Ohm's law, where a voltage applied across a device's conductance results in a current, and Kirchhoff's current law (KCL) we can sum along the columns of our memory crossbar to perform matrix multiplication in O(1). These memory crossbars can then abstracted into cores as shown in Figure 2d, where system level approaches similar to systolic arrays [3] or DNN accelerators [5] can be used.

If successful, in-memory computing promises to solve many of the engineering challenges that the modern memory hierarchy faces with regards to data transport. In recent years, new emerging devices have made huge milestones on their way to commercial viability. High density macros have been fabricated [22], and used in the implementation of highly

efficient neural networks [23]–[25]. However, these new emerging memories face many challenges of their own preventing them from widespread commercial use. In this article, we will examine some of these challenges and provide an overview of the recent developments both from technology as well as circuits and systems perspectives.

# System needs for memory-centric neural network workloads

The demand for in-memory computing is ever growing as the state-of-the-art designs for computer vision, natural language processing, and RL continue to have larger models with more computation and performance that require months of training time on clusters of custom accelerators. At the same time advances in microrobotics require smaller area footprints and power budgets. These different workloads require the same thing: energy-efficient computing. As these applications begin to outpace the computers we have to perform these tasks, we will need to look at fundamentally different approaches of computing.

At the start of the current surge in deep learning, AlexNet [26] was trained and implemented using a pair of GTX 580 graphics processing units (GPUs) and custom CUDA code. Soon after larger and larger models requiring more hardware became the new state of the art, as VGG [27] and ResNet [28] required multiple GPUs to train in a reasonable amount of time. Today there is an abundance of deep learning frameworks and hardware designed for machine learning readily available. These tools and hardware have propelled deep learning research, making it far more practical to design and test large deep learning models. Despite these efforts, state of the art models in natural language processing, computer vision, and RL require massive amounts of memory and computation that can no longer be run on consumer grade hardware. For example, OpenAI has used RL to beat professional players at Atari, GO, and most recently StarCraft 2 [29]. Jouppi et al. [3] claim that training an agent requires 44 days of training with 32 third-generation TPUs. Training such a model is extremely expensive and impossible for anyone without access to enormous compute power. While inference for this model can be run on a typical GPU, newer models in NLP [30] and computer vision [31] require 4 billion and 1 billion parameters, respectively.

At the same time, the interest in machine learning in mobile and edge platforms is constantly increasing and hardware accelerators and software frameworks are being developed specifically for these platforms. While great progress is being made to run small models on resource and power constrained hardware, CMOS limitations and the von Neumann bottleneck will limit the capability of edge hardware.

# Overview of emerging nonvolatile memory

There are many properties to evaluate when considering new emerging devices for in-memory computing. Of course we expect these devices to be nonvolatile with good retention as well as having a resistive state that can be used for in-memory computing. Besides these qualities we also must consider read and write times, read and write energy, read and write voltage, endurance, area, and the number of distinguishable states per cell. We present an exhaustive overview of these metrics for in-memory computing in Table 1. We focus our attention to the four leading candidates for in-memory computing and compare them to the current standard used in commercial products: SRAM, DRAM, and Flash. In their current state, none of the emerging devices display all desired characteristics. In a different review article, Yu and Chen [21] and Yu [32] identify the ideal characteristics for these devices.

We group these properties into four major areas: 1) density; 2) read performance; 3) write performance; and 4) reliability. The importance of the device properties is very application-specific. For example, as we discuss later this in work, the write performance and write endurance of these devices are less important if the devices are used in a network only performing inference. However, in a network that is being trained, high write energy can be the primary source of energy consumption, and it can be a significant system challenge.

- *Density*: The density of these NVM technologies is the product of the number of cells per unit area and the number distinguishable states per cell. The density of eNVM is on the order of 10*F*<sup>2</sup>, whereas SRAM is over 150*F*<sup>2</sup>.3D integration of eNVM on the back end of line (BEOL) process is under investigation; where the density can be pushed even further. However, some of the constraints in BEOL processing, most importantly the low temperature requirements, continue to be challenging.

- Read performance: Read performance for CIM constitutes memory access, memory transport,

| Memory    | Ref  | Density            |     | Read    |       |        | Write   |               |        | Reliability |           |

|-----------|------|--------------------|-----|---------|-------|--------|---------|---------------|--------|-------------|-----------|

| vieniory  | Rei  | Area               | Bit | Voltage | Time  | Energy | Voltage | Time          | Energy | Retention   | Endurance |

| SRAM      | [21] | 150 F <sup>2</sup> | 1   | 1       | 1ns   | 1fJ    | 1       | 1ns           | 1fJ    |             | $10^{16}$ |

| DRAM      | [21] | $6 F^2$            | 1   | 1       | 10ns  | 10fJ   | 1       | 10ns          | 10fJ   | 64ms        | $10^{16}$ |

| Flash     | [21] | $10 \ F^2$         | 2   | 10      | 50ns  | 10pJ   | 10      | 1ms           | 1nJ    | 10y         | $10^{5}$  |

|           | [21] | $50 \ F^2$         | 1   | 1.5     | 10ns  | 1pJ    | 1.5     | 10ns          | 100fJ  | 10y         | $10^{15}$ |

| MRAM      | [33] | $75 \ F^2$         | 1   | 1.2     | 2.8ns | 0.7pJ  | 1.8     | 20ns          | 4.5pJ  |             |           |

|           | [34] | $0.358 \mu m^2$    | 1   | 1.2     | 30ns  | 14.6pJ | 1.2     | 30ns          | 17.4pJ |             |           |

|           | [35] | •                  | 1   | 1.2     | 3.3ns | 0.3pJ  | 1.2     | 3ns           | 0.6pJ  |             |           |

|           | [21] | 30 F <sup>2</sup>  | 2   | <1      | 10ns  | 1pJ    | 3       | 50ns          | 10pJ   | 10y         | $10^{6}$  |

| PCM       | [36] |                    | 2   | <1      | <10ns | 0.1pJ  | 3       | 100ns         | 10pJ   | 10y         | $10^{5}$  |

|           | [37] | $50 \text{ F}^2$   | 2   | <1      | <10ns | 0.5pJ  | 3.3     | 300ns         | 30pJ   | 10y         | $10^{8}$  |

|           | [21] | $12 \ F^2$         | 2   | <1      | 10ns  | 1pJ    | 3       | 10ns 10pJ 10y | 10y    | $10^{6}$    |           |

| RRAM      | [38] | $100nm^{2}$        | 1   | <1      | 10ns  | 10fJ   | 1.5     | 10ns          | 100fJ  | 10y         | $10^{7}$  |

|           | [39] | •                  | 1   | < 0.5   | 5ns   | 1pJ    | <1      | 10us          | 1nJ    | •           | •         |

|           | [40] | •                  | 2.3 | 0.2     | 23ns  | 1.76pJ | 3       | 50ns          | 10.1pJ | 10y         | •         |

|           | [21] | $40 \ F^2$         | 2   | 3       | 10ns  | 1fJ    | 3       | 10ns          | 100fJ  | 10y         | $10^{6}$  |

| FeFET-RAM | [41] |                    | 1   | <4.5    | <25ns |        |         | <500ns        |        | 10y         | $10^{5}$  |

|           | [42] | •                  | 1   | 0.68    | 3ns   | 0.28pJ | 0.4     | 0.55ns        | 4.82pJ |             | •         |

|           | [43] | $2.7 \mu m^2$      | 1   | 1.64    | •     | 15.5pJ | 0.8     | 0.55ns        | 15.0pJ |             | •         |

and multiply-and-accumulate (MAC) operations. It is even more important when only inference is being performed as all power dissipation will come from reads.

- *Write performance:* As we will discuss later, write performance is more important when training crossbar arrays since they will be updated very frequently and most of the times the write energy for eNVM devices is much higher than read energy. It is quite intuitive to understand that memory solutions that are inherently nonvolatile will require higher write energy to change states. Often, the devices require high write voltage as well (2–5 V) and they are harder to integrate on the logic process. However, compared to eFLASH where write voltages are often 20 V and higher, the current generation of eNVM require significantly lower write voltages and demonstrate scaling paths for voltage and process compatibility with logic.

- Reliability: Most devices have retention on par with commercial flash processes. However, the endurance of these devices varies greatly. As we will discuss later, endurance is important when implementing training since the devices will be updated frequently.

#### Resistive random access memory

Resistive random access memory (RRAM) (often called ReRAM) is a filamentary device that switches between a high resistance state (HRS) and low resistance state (LRS) based on the direction of current applied across the two terminals. The HRS and LRS in RRAM are achieved by forming and destroying a filament inside the insulator material of the device. By creating and destroying this filament we can lower and raise the resistance of the device by orders of magnitude. The transition from HRS to LRS is called the set process where the device allows more current to flow emulating a digital "1." The transition from LRS to HRS is called the *reset* process where the device is less conductive and results in less current across the terminals. Since a read and write operation both apply voltage on the two terminals, the read voltage must be much lower to not alter the state of the device and perform a destructive read. In the 1T1R (1 transistor and 1 resistor) structure, the read voltage is controlled by using a small voltage on the gate of the transistor.

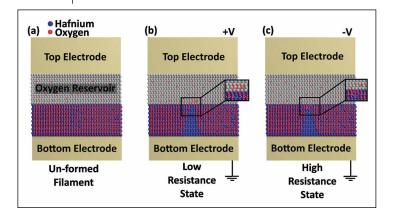

Although there are different types of RRAM, the most successful is metal-oxide RRAM [44]. It has been used in the implementation of a commercial RRAM macro [45] as well as in a trainable neural network [25]. The alternative, conductive bridge RAM (CBRAM), offers a higher HRS to LRS ratio, but has worse endurance and retention. For this article, we will focus on metal-oxide RRAM. The device structure of metal-oxide RRAM simple, comprising a top metal electrode, a bottom metal electrode, and a transition metal oxide (TMO) layer in-between as shown in Figure 3. RRAM initially starts in a pristine state and most devices must undergo formation prior to being used as intended. During formation, an initial large

Figure 3. (a) Fabricated device. (b) RRAM after forming and device in the LRS. The conducting filament is formed and will be used to toggle between the LRS and the HRS. (c) RRAM after being reset into the HRS. The tip of the filament is reoxidized which increases the resistance of the cell. (Source: Matthew West, Georgia Tech.)

voltage is required to create an electric field capable of knocking oxygen atoms out of the insulator's lattice and creating vacancies that make up the conductive filament leading to the LRS. The formation process only needs to be done once taking the device from its initial pristine state which has a resistance larger than the HRS of the device post formation.

After formation, it is assumed that the conductive filament is created with sufficient oxygen vacancies in the insulator such that the large formation voltage will not be required again. From the formed LRS state, the device can switch back to an HRS state during the reset process by recombining the oxygen atoms with the vacancies making up the conductive filament. Once the filament is ruptured its resistance will increase, however, the distance of the ruptured filament can cause cycle-to-cycle and device-to-device variation because of the inconsistent location where the filament is ruptured. The way the device is reset depends on the materials used as the insulator. The device can be reset as a unipolar or bipolar switch. A unipolar device is reset based on the magnitude of the pulse applied across the device. A bipolar device is reset based on the polarity of the applied voltage. Most device fabricated at large scale use the HfOx RRAM which is a bipolar switching device. However, there are advantages to using a unipolar device since it only requires a diode as a selector rather than a transistor.

Although used primarily as a binary device, some work has been shown to demonstrate multibit or even analog state in RRAM. As many as five states have been demonstrated using HfOx RRAM [46]. If binary encoding is used for multiple bits, then additional CMOS circuitry is needed for add and shift logic. However, achieving multiple states is difficult due to the abrupt switching behavior, low on/off ratio, and device-to-device and cycleto-cycle variation. Some techniques have been explored to achieve multiple states in the device. Different pulse and programming schemes can be used to better control the exponential behavior of set resistance states [47]. Another technique [48] has demonstrated analog control of the RRAM using the slower reset behavior.

#### Phase change random access memory

Modern phase-change memory (PCM) devices enjoy relative maturity and have been explored for several decades. Early work by Ovshinsky [49] demonstrated the ability of phase-change materials to store data, and a subsequent discovery by Yamada et al. [50] demonstrated a class of materials the stored state of which could be overwritten many times and switched quickly enough for storage devices based on these materials to be competitive with the then-dominant memory technologies. Phase change materials have since become the critical component in optical storage media, with an additional research interest in these materials for use in new types of electronic storage devices having been revitalized [51].

PCM consists of memory devices that take advantage of the ability of certain materials to repeatably transition between a crystalline phase and an amorphous phase. For a material to be useful in typical PCM applications this transition should be accompanied by a marked change in at least one measurable quantity. Memory systems constructed from these materials typically leverage either a large contrast in reflectivity, as in the case of optical storage, or in resistivity, as in the case of the electrically operated phase-change random access memory (PCRAM), where *contrast* here refers to a change in the measured quantity as observed in the crystalline material versus that observed in the amorphous material [51]-[54]. This section will proceed to discuss resistive PCRAM and will pay particular attention to the Ge<sub>2</sub>Sb<sub>2</sub>Te<sub>5</sub> (GST) chalcogenide material that finds extensive use in PCRAM, e.g., [36], [55], and [56]. A discussion of material and device properties in the context of memory applications will be followed by a brief survey of quantifiable PCM parameters.

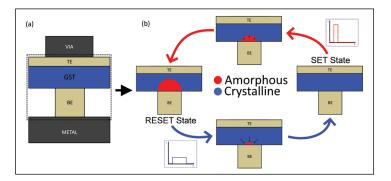

PCRAM devices are made up of a layer of glass chalcogenide material, hereafter assumed to be GST, sandwiched between two electrodes, as shown in Figure 4. These electrodes may be used to write or read the cell state. Crystalline GST is more conductive than amorphous GST, and the conversion of the volume of GST within the cell between these phases causes a resistance change that is typically at least one or two decades [53], [57]. State switching is accomplished via joule heating by passing current through the cell, while readout is typically done by placing a small voltage across the device and measuring current [58]. This is shown in Figure 4. The two phase-transition write processes, the crystallization-driven SET toward lower cell resistance and the melt/quench RESET toward higher resistance, will now be discussed in more detail.

Crystallization of amorphous GST is a temperature-dependent process [59], [60]. Crystal growth velocity first increases exponentially with temperature until a relatively hot transition point at which the relationship between crystal growth and temperature slows down, with growth velocity eventually reaching a peak and then decreasing with further increases in temperature. Therefore, Joule heating to an intermediate temperature (≈400 °C) leads to rapid growth in the volume of crystalline material in a given cell and tends to reduce the net resistance between the two contacts, giving rise to a SET operation that consists of a prolonged current pulse with limited magnitude. Heating past the rapid crystallization temperature eventually results in melting of the GST material at ≈600 °C. Thus, a RESET operation involves a large-magnitude current pulse followed by a quick quench, to solidify the material in an amorphous state, which is accomplished by a sharp trailing edge. The relatively high-temperature transition point at which the GST crystal growth rate ceases to increase exponentially helps to resolve the dilemma that arises from the conflicting requirements for a PCM material, i.e., that it must crystallize quickly when desired but must crystallize only very slowly, and in the ideal case not at all, when not intentionally heated.

Without an additional mechanism, the voltage required to produce sufficient Joule heating to achieve rapid crystallization from the high-resistance cell state

Figure 4. (a) Typical "mushroom cell" PCM layout, showing top electrode (TE), GST, and bottom electrode (BE). Proportions follow TEM images of a recent device demonstrated in [36]. (b) Statetransition diagram showing the PCM cell in the RESET state, with the BE plugged by high-resistivity amorphous material, and in the SET state, with the volume of GST material switched to the conductive crystalline phase. Partial-set, bottom-middle, is typical of MLC while partial-reset, top-middle, is less feasible.

would be problematically large. However, PCM materials exhibit a threshold-switching behavior defined by a dramatic increase in current flow through the amorphous-state material under a sufficiently strong electric field [49], [61]. This switching is a high-field effect distinct from the previously mentioned phase-mediated memory switching. As threshold switching is induced by field strength the voltage at which switching occurs is nonstationary and depends at least on the thickness of the amorphous layer [62]. Notable is that this effect has a non-negligible temporal component, exhibiting both a delay time, between application of the switching voltage and the large current increase, and a recovery time, between the cessation of voltage application and the corresponding increase in resistivity, both on the order of tens of nanoseconds [63]-[65]. When biased subthreshold, the amorphous resistance still depends on field strength and cells are in an approximately linear IV region only for applied voltages of up to about 300 mV, above which the IV dependence becomes exponential [66].

After cessation of Joule heating an additional transient effect leads to a slower power-law increase in off-state resistance which is accompanied by a similar increase in threshold voltage [63], [67]. This so-called resistance drift may be explained by the time-dependent structural relaxation of the

amorphous-state material [68]. A more complete elaboration on the time and temperature dependence of the amorphous phase resistance may be found in [69] or [70]. In a non-CIM application with two-state (binary) PCM cells this drift is less important as it tends to broaden the interstate gap. An associated property of GST-based devices is the presence of a 1/*f* noise current which is nearly two orders of magnitude greater in the amorphous state as compared to the crystalline state [71].

Having laid out the key physical properties of PCM, we proceed to discuss how these properties practically impact PCM devices. Crystallization occurs over time, during which the cell is held at an intermediate temperature. Recall that the melt and quench procedure can be very fast, and in fact the falling edge must be very fast to prevent recrystallization. This means the SET operation traditionally requires hundreds of nanoseconds and is much slower than the RESET operation which can occur in tens of nanoseconds. This long SET operation also means the write time dwarfs the read time. Furthermore, the required Joule heating means that the write operations are energetically costly. This is again in contrast to the read operation, which must occur at just a few hundreds of millivolts to avoid threshold switching and remain in the linear operating region of the cell.

Recompense for the difficulty of writes is that the written states are nominally of high quality with a substantial on/off ratio of at least 100× in measured devices [36]. A consequence of this is that it becomes feasible to program cells to intermediate states between the fully on and fully off conditions, leading to increased storage density through MLCs [58], [72]. Both MLCs and CIM (via current summing across multiple cells) imply a nonbinary range of output states and thus depend on precise control of cell resistance, which is not trivial for two reasons. First, there are many degrees of separation between the input variable during programming (i.e., current or voltage) and the output (which is finally measured as resistance). Second, there are the previously discussed resistance drift and 1/f noise in the amorphous material, which become problematic for applications that depend on the discernibility of several intermediate states despite being mostly benign with respect to the binary memory application.

The first challenge may be approached by using feedback-based write algorithms. In these schemes, a SET is accomplished with a train of write pulses, where the properties (such as amplitude, width, and trailing edge length) of each subsequent write pulse are modulated based on a resistance measurement that is made after the previous pulse [58], [72]–[74]. Feedback cannot be taken during the write pulse itself due to threshold switching, and there must be some delay after the write, prior to the low-voltage read, to ensure that normal resistance has resumed. The time for each cycle of a write algorithm is therefore determined by the delay and recovery time of threshold switching on top of the minimum pulse time to heat the material and cause some phase transition.

The second challenge, which may be summarized as the poor resistive accuracy of the amorphous material, does not present application-agnostic circuit-level solutions. As mentioned, the effect of this poor accuracy on purely binary memory is expected to be minimal, and indeed more in-depth noise analysis shows that the 1/f noise component has only a slight impact on RESET-state readout relative to other sources of error [75]. In the context of MLC, these problems may be understood as components of a broader issue, namely the decoupling of the measured quantity (cell resistance) from the underlying stored state (relative volumes of crystalline and amorphous material). This has motivated the development of alternative cell-state metrics that, relative to the lowfield resistivity metric, more directly audit the amount of amorphous material in a cell by measuring with higher subthreshold fields [76], [77]. Cell readout under these schemes implies a voltage bias that varies with cell state meaning they cannot directly be used in current-accumulative CIM applications.

In light of technological accuracy limitations, applications that are inherently error-tolerant or that rely on CIM only for low-precision components of a computing task are ideal candidates for acceleration via CIM with PCM. Recently presented examples of such robust applications include compressed sensing [78] (in which the linear algebraic operations associated with both compression and recovery of signals may be accelerated with approximate in-memory compute with PCM) and the solving of linear equations using deliberate mixed-precision techniques [79]. Note that in the first example the error due to the inaccuracy of the PCM is accepted, since some error in the reconstructed signal (an image) is tolerable, while in the second example a high-precision computing unit complements the CIM system in an iterative refinement scheme so that the resultant error is only that of the high-precision unit. An alternative approach is to attempt to mirror biological synapses by leveraging the analog (i.e., continuous) nature of the increases and decreases in resistance that can be accomplished in a PCM cell [80]. Continuous crystallization is also exploited in [81]. A more basic approach is to select a lower precision version of the computing task and hide any remaining error behind the built-in robustness of that task, as is the case with binary neural networks (BNNs) as suggested in [36].

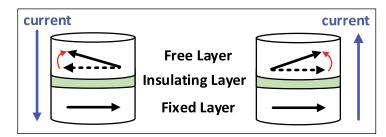

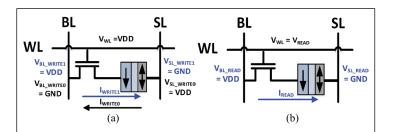

# Spin torque transfer magnetic random access memory

A more mature technology for resistive memories is the spin transfer torque-based RAM. The Spin torque transfer magnetic random access memory (STT-MRAM) or MRAM bitcell consists of one access transistor and one magnetic tunnel junction (MTJ) where a single bit of information is stored. An MTJ is formed with two ferromagnetic CoFeB-based layers and one insulating layer (MgO) in between [82]. One ferromagnetic layer is called a fixed layer because its magnetic moment is fixed to one direction. The other ferromagnetic layer is called a free layer since the direction of magnetic moment can be changed based on the direction of current flowing across the MTJ.

Figure 5 describes how the direction of magnetic moment in the free layer changes based on the current across the MTJ. Figure 5 shows how the direction of magnetic moment in the free layer changes from (a) antiparallel to parallel and (b) parallel to antiparallel direction compared to the direction of magnetic moment in a fixed layer. Since the fixed layer acts as a spin polarizer, the spin polarized electrons that pass the fixed layer exerts the torque on the magnetic moment in the free layer and causes a flip in the direction of the magnetic moment in the fixed layer as shown in Figure 5a. When the current flows from the fixed layer to the free layer as shown in Figure 5b, the electrons with opposite spin are reflected back from the fixed layer and exerts a torque that changes the direction of the magnetic moment of the free layer to an antiparallel direction with respect to the magnetic moment in the fixed layer. The alignment of the magnetic moment in the fixed and free layers determine the resistance across the MTJ. When the magnetic moments in the two layers are antiparallel to each other, the resistance across MTJ is high.

A low resistance is achieved when both the magnetic moments are parallel to each other. The high/

Figure 5. Direction of magnetic moment in free layer changes from (a) antiparallel to parallel (b) parallel to antiparallel to the direction of magnetic moment of fixed layer. The arrow in the free/fixed layer indicates the direction of magnetic moment.

low resistance is mapped to 1/0. The bias conditions applied for the write and read operations are shown in Figure 6. As shown in Figure 6a, the write operation is bidirectional. In the case of writing a 1, the BL and the source line are set to supply voltage (VDD) and ground (GND) and the write current flows from the fixed layer to the free layer of the MTJ. The biasing condition for writing a 0 is the opposite and is shown in Figure 6a. In the case of read operations, the wordline is asserted to VREAD, and the BL and the source line are set to VDD and GND, respectively. This causes a weak current to flow across the MTJ and the resistance state is sensed using either a constant current scheme or a BL discharge scheme [83]. As the technology continues to mature and move from research to manufacturing, larger arrays and systems are being demonstrated.

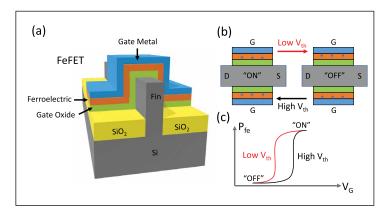

# Ferroelectric field effect transistor-based random access memory

Ferroelectric FET (FeFET) is a nanoelectronic device composed of a traditional MOSFET or FinFET and an additional special layer of ferroelectric (FE) material, which is integrated into the stack of gate

Figure 6. STT-MRAM cell schematic of (a) write and (b) read operation.

terminal [84]. Figure 7a illustrates the 3D structure of a FeFET built on FinFET. The FE materials are usually lead zirconium titanate (PZT) [85] or hafnium zirconium oxide (HZO) [86]. The latter one is compatible with CMOS process while the former one does not. Note that the spontaneous polarization of the FE layer is reversible under a certain electric field applied in the correct direction. The polarization depends on the current electric field and its history, resulted in a hysteresis loop. Such a feature of FE layer induces a FeFET to switch "on" at a high voltage and "off" at a low applied gate voltage (Figure 7b and c). It is nontrivial to clarify the definition of "FeFET" here since the FeFET is not the only device that stack FE layer on the gate of a FET and such a semiconductor structure can also operate in different operating modes. For example, a negative capacitance FET (NCFET) with the same structure operates in "steer switching mode" and usually aims at eliminating hysteresis for faster switching [87]. Here, we emphasize that an FeFET exhibits the property of hysteresis that can be utilized in different applications. FeFET has been explored in multiple application levels of computing systems, such as components of traditional analog circuits [87], digital circuits [88]–[90], nonvolatile memories [42], [91], and FPGA [92], [93].

Recently, FeFET has been considered as an emerging device used as a memory structure (FeFET RAM) particularly for machine learning hardware and neuromorphic computing. It was applied to the accelerator architectures of both digital and analog neural networks [94], [95]. In these works, FeFETs are utilized to design synaptic crossbar arrays such as

Figure 7. (a) 3D structure of FeFET, (b) "on" and "off" states of FeFET with different threshold voltages, corresponding to the polarity states of FE layer shown in (c), and (c) hysteresis in terms of polarity and gate voltage.

RRAM crossbar structure. RRAM-based architectures are troubled with high write energy and sneak paths. The three-terminal structure of FeFET provides better write and read power consumption [94]. Write operations consume power only when FE layer capacitance VG gets charged, which is much lower than the crossbar of RRAMs. For the accelerator of a binary convolutional neural network (CNN), the cell of an FeFET crossbar array consists of two FeFETs and two access transistors. It performs the XNOR operation between the input bit and the weight bit stored in the two FeFETs. Such a design of FeFET-based crossbar exhibit power reduction of both read and write operations when compared to the same designs based on RRAM and CMOS [94]. In addition to acceleration of BNN, FeFET-based nonvolatile analog memories are a promising solution to the future accelerator of DNN with analog weights. An FeFET synaptic weight is capable of achieving multibit operation by leveraging the partial polarization switching dynamics of multidomain FE Hf<sub>x</sub>Zr<sub>1-x</sub>O<sub>2</sub> thin films [95].

Furthermore, FeFET has been recently explored in SNNs, another neuromorphic computing paradigm that is more biomimetic than DNN. In these scenarios, FeFETs are adopted in the circuits of bioinspired neuron model, instead of synapses. A spiking neuron with excitatory and inhibitory interfaces can be implemented with a relaxation oscillator based on FeFET [96]. The proposed circuits employ the hysteresis of an FeFET and a traditional NMOS transistor to periodically charge and discharge a load capacitor and generate spikes of voltage. Such a two-transistor compact design of silicon neuron is capable of modeling multiple neural dynamics that have been observed in cortical and thalamic neurons when fed with excitatory and inhibitory synaptic inputs [97]. These various neural dynamics are demonstrated to be useful in a FeFET-based SNN that solves optimization problems [98]. Due to the flexible neural dynamics provided by FeFET-based spiking neuron it also has the potential to become a promising circuits design for other applications in neuromorphic engineering, such as neural interfaces and biohybrid neural circuits [99], [100].

# Overview of in-memory computing

#### Matrix multiplication in eNVM crossbar arrays

Modern deep learning techniques such as CNNs and RNNs contain a workload of almost entirely matrix multiplication  $(\vec{y} = W\vec{x})$  [101]. In traditional

#### IEEE Design&Test

von Neumann machines, both the feature data  $(\vec{x})$  and matrix weights (W) are transported from the main memory to the compute units, where the MAC operations are performed, and after which, the results  $(\vec{y})$  are transported and written back into main memory. For this procedure, prior work has shown that the energy cost of reading and transporting data from memory to logic greatly outweighs the cost of the MAC [4], [5], thus motivating in-memory computing.

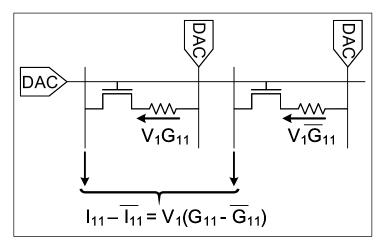

In-memory computing seeks to perform the MAC operation in a crossbar structure using Ohm's law and the nonvolatile conductance state provided by ReRAM or other emerging memories. Using this technique, each weight of the matrix  $(W_{ij})$  is programmed as a conductance to a cell in the crossbar and each value of the vector  $(\vec{x}_i)$  is converted to voltage and applied to the rows of the memory crossbar. By Ohm's law, the current through each cell is proportional to the product of the programmed conductance  $(W_{ij})$  and applied voltage  $(\vec{x}_i)$ . By KCL, the resulting currents summed along the columns of the crossbar are proportional to the product of the matrix and vector,  $(\vec{y})$ . Under this procedure, the only data transport required for matrix multiplication is the feature vector  $(\vec{x})$  and result  $(\vec{y})$ . Therefore, in-memory computing is positioned in such a way that it eliminates the majority of data transfer and thus the energy cost of DNNs.

#### Analog versus digital in-memory computing

The motivation for eNVM has come from multiple directions, and as a result, two different models for the memories have emerged: 1) digital and 2) analog. These memories were originally intended to be used as a digital, low latency, and energy-efficient alternative to existing nonvolatile memory in the traditional memory hierarchy. Later on, HP labs created a metal-oxide RRAM and claimed it had memristive properties [102]. They intended to use this device as an analog memory that could serve as a synapse or weight in neural networks.

There are several tradeoffs between the two models. The main tradeoff is performance versus feasibility. On the one hand, the analog model has numerous performance advantages over the digital model. In the ideal case, the analog model can store any positive, continuous value between its on and off resistance states. Such a device could be used to store high precision values without needing several devices to represent a single weight. Given that traditional neural networks contain both positive and negative weights, two cells are required to represent a single weight since the conductance state of eNVM cannot be signed. The value of the weight is represented as the difference of the conductance of two cells as shown in Figure 8. Naturally, this enables very high density, but also has implications for both power and performance.

However, due to device-to-device variance, cycleto-cycle variance, and limited on–off resistance ratio using the eNVM as an analog memory has proven difficult. Hence most implementations today focus on digital implementations using write–verify circuitry. Recent work [36] has demonstrated PCRAM devices with a resistance standard deviation of 3.5% and on-to-off ratio of >10<sup>2</sup> using this technique. With such a device, it is plausible to enable MLC. An important distinction between MLC and analog memory is that while an MLC has multiple states, it still requires ADC to distinguish the states.

Shafiee et al. [103] encode weights in a offset format so that negative weights can be represented. Given that the devices can perform only multiply and accumulation in the crossbar, there is no way to naturally represent a negative value. Therefore, a bias is applied to all weights before being written to the crossbar, and then subtracted after the rows are read. Since many rows are turned on and accumulated along the same column, the bias is subtracted from the final result for each row that was turned on. For example: in a signed 8-bit 2's complement format, -128 would be written to the crossbar as 0. After being read out during compute-in memory, the bias of 128 would be subtracted.

Figure 8. 1T1R circuit with a differential pair for signed weights.

Peripherals for in-memory computing

CIM architectures promise to achieve certain advantages over traditional architectures in efficiency and throughput by replacing digital addition with an analog-domain alternative. This implies that the binary bitcell readouts typical of traditional memory macros become multiple-bit readouts in CIM arrays, and the sense-amps typical of traditional memory accordingly become ADCs in CIM architectures. Furthermore, certain technology candidates for CIM require specific bias points for read and/or unusually large power for write. Meeting these added requirements without sacrificing the performance

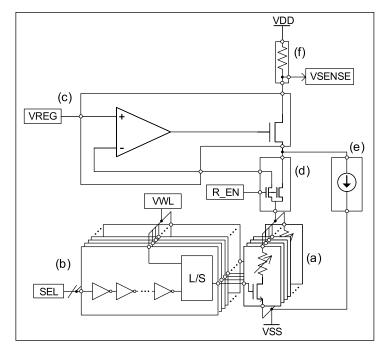

Figure 9. Readout peripherals for a resistive CIM array shown as a block diagram of individual functional units. Examples of the functional makeup of each unit are shown inside each block, although the actual implementations will vary based on system requirements. (a) Column (that is, a group sharing a BL) of resistive memory cells with access devices. (b) Wordline driver with level-shifting. (c) Biasing/BLdriving circuit formatted as a voltage regulator. (d) High-V<sub>t</sub> pass transistors that may be necessary to protect the BL driver from write pulses. (e) Bias current used to improve the stability of the voltage regulator in (c) and linearize the current sense device used to implement. (f) Current-sensing effective resistance. Note that some designs will use the gate of the regulator's pass device shown in (c) as the measurement point for a voltage representing memory cell current.

benefits promised by CIM will require novel peripheral circuitry. This section will provide an introduction to the readout peripheral design space for CIM by detailing a representative set of requirements and proposing how they may be satisfied. We focus on readout circuitry up to the ADC, omitting a detailed discussion of both write circuitry and ADC composition since the former is intimately dependent on choice of memory technology and the latter represents a massive variety of design choices.

The functional components involved in readout for CIM are shown in Figure 9, a new figure which expands on and has been inspired by the work of Close et al. [104], Kwon et al. [105], and Athmanathan et al. [106]. We propose that the readout process may be thought of as consisting of three stages.

- A *selection* stage during which the cells are activated via a change in wordline state.

- A *biasing* stage during which the selected cells are forced into the correct operating region, so that they produce some readable analog value.

- A *conversion* stage during which the analog value is captured into a digital reading.

The selection stage is accomplished via a buffer chain subject to two functional requirements: it must be sized to drive the wordline capacitance within a required time-frame, and may additionally be required to provide voltage conversion or protection between the core logic synchronizing the computation and the gate voltage of the cell selector devices. The degrees of freedom for wordline driver implementation include the choice of voltage level-shifting scheme, [107]–[112], and the choice of stage-over-stage sizing in the buffer chain [113]. The tradeoff space is speed, typically accomplished with a many-stage buffer and converter design (closer to e-scaling), against power and area. Broadly, these design constraints for CIM wordline drivers match those of the well-explored wordline driver design spaces for traditional memory technologies, including DRAM [108], SRAM [107], [109]–[111], and Flash [112]. The wordline driver is modeled by component (b) in Figure 9.

As shown in Table 1, typical implementations of Flash, STT-MRAM, PCM, RRAM, and FeFET-RAM require high voltage and potentially significant current during write. This encourages a low selector device channel resistance which may be accomplished by driving the gates of these selector devices far above typical core logic voltages. For the buffer to survive these operating conditions at minimum the output devices must be able to handle these higher voltages. Typically, this will mean the minimum channel length of these transistors must be increased, which will in turn significantly increase the gate area, and capacitance, of transistors sized to rapidly charge the wordline [112]. Alternatives include cascoded output devices that each only see a portion of the high voltage or a series of moderate voltage step-ups. Any of these will result in increased area and energy usage. Some other technological requirements, e.g., for an especially low gate voltage during read to avoid read-disturb, do not risk buffer transistor breakdown and are therefore significantly easier to accommodate.

Having selected cells, the next task is to bias the cells into an appropriate operating region so that their stored state, typically resistance, may be measured. This is shown in Figure 9c. While other biasing schemes are possible, the most straightforward and typical technique is to apply a specific voltage across the selected cells, converting cell resistance to current [105]. If the state of each cell is expressed as a conductance, the resultant current due to this voltage will be proportional to the sum of the cell states. Constant-voltage biasing therefore directly implements current summing. The circuitry involved in applying a constant-voltage bias across memory cells is similar to that involved in typical voltage regulator designs, with a few additional requirements: the biasing circuit must be able to tolerate high voltage at the BL (if required for write), tolerate widely variable load resistance, and sense the output current.

The first of these additional requirements parallels the voltage-tolerance requirement of the wordline driver. However, the BL driver does not swing across the full output voltage range but instead holds voltage nearly fixed while scaling current delivery to match the load. Additionally, the parasitic BL capacitance, which typically looks into the memory cell (modeled as a variable resistor) may be lower than the wordline capacitance, which typically looks into the gate of a fairly high-current transistor. These factors combine to mean that adding series channel resistance via a protection pass transistor can tolerate high voltage on the BL and can be turned off during write, can be less deleterious to biasing speed and efficiency. This pass device may be inserted between the output of the voltage regulator and the BL. Additionally, if significant cell current may be expected to pass from the regulator to the BL through the pass device, a separate low-current "voltage-sense" pass device may be used for the voltage feedback component of BL voltage regulation. This structure is shown in Figure 9d.

The widely variable load resistance results from a design goal of resistive memory. Resistive memory cells should exhibit a high on/off ratio, meaning that their stored state should have a high dynamic range to maximally separate each nominal state and reduce error. This has the potential to create two issues. Practically, the voltage regulator that biases the cells will likely incorporate negative feedback to establish a precise BL voltage, and may therefore require compensation. This compensation may occur at the output for high performance, and the location of this output pole in frequency will be sensitive to the small-signal impedance at the output of the regulator. In order-of-magnitude terms, as an example, if ten binary memory cells each swing 100× from off-state to on-state, the load impedance seen at the output of the regulator will swing  $1000 \times$ , i.e., 60 dB. Compensating for the highest-impedance extreme will therefore be likely to hinder performance at the lowest-impedance extreme, which is exactly where a quick response is required as the load will be demanding the most current when most cells are on-state. Conversely, under-compensating to achieve a quick response for the largest loaddump may cause stability issues when few cells are on. The other issue is simply that reliably sensing current across several decades can be challenging.

Both of these issues may be addressed by introducing a current-bias circuit, component (e) in Figure 9, to establish a minimum output current above what would be set by the memory device alone [105]. This bias current can be set to place the expected current range that will be read across a linear region of the current-sensing device, if needed. The bias circuit may be expected to decrease output impedance first of all simply by increasing the minimum current through the output device of the voltage regulator. Additionally, the bias circuit may itself be designed to have a low small-signal input impedance to directly limit output impedance of the regulator.

The remaining challenge to discuss in the context of the bias circuit is current sensing, component (f) of Figure 9. The canonical technique for sensing current is to add a low-value effective resistance in series with the load then amplify the voltage drop across this effective resistance. Typical pure-CMOS

implementations have accomplished current sensing via the control-side of a current mirror or cascoded current mirror, that is, with a diode-connected transistor [104]-[106]. In particular, if this current-sense transistor is cascoded (or source-degenerated), the voltage headroom required by the sense device added to that required by the output device of the voltage regulator can be significant. In power-sensitive designs, this may preclude more efficient schemes that would first reduce the core voltage using a capacitive or inductive converter before finally setting the BL bias with a linear regulator. Alternatively, adding several series devices between the regulator's output transistor and the rail may reduce the effective transconductance of this transistor, requiring its size to be increased to recover gain and improve regulation. These factors may motivate a simpler scheme where the gate voltage of this output transistor is itself used as the current-sense metric.

The final step, analog to digital conversion, is application-specific. The maximum useful resolution is established by the minimum of the precision of the memory devices (inversely proportional to their variance) and the expected number of distinct output states to be measured. It may be that the current handling of core devices in a technology limits the maximum number of on-state devices (at a given minimum bias voltage) to a small number so that only this small number of distinct states needs to be measurable, or alternatively it may be that the variance of the current conducted by the memory devices limits the number of devices that may be measured before variance may be expected to cause unacceptably frequent errors.

Circuit-level ADC limitations are due to power and area restrictions. Area usage is a critical factor in CIM because memory arrays can be very dense while precise peripherals can be bulky. In a typical design, peripherals will be pitch-matched along both axes. While wordline drive circuitry can be very simple, the BL components will quickly exceed the pitch of a single column of memory cells. This limits the ADC and BL driver complexity that is suitable for a scalable design. While we will not fully explore the available options for ADCs, consider that the special requirements for ADCs for CIM are that they have a high throughput at a relatively low bit depth (3- to 6-bit designs are typical) and that their complexity and efficiency is managed so that throughput may be increased by tiling many of them adjacent to the array.

#### Low precision peripheral designs

As we will discuss in the "CIM-based accelerator architecture" section, it is possible to reduce the complexity of peripheral circuits by reducing the bit precision used in both the input features and weights of the network. While this does come at a cost in application performance, several works have shown that this is minimal for less complex applications. As a result, these works can achieve significantly higher throughput and lower energy per operation [13]. However, it should be noted that for larger and more complex problems, higher precision is often required to achieve respectable results.

One such approach is to use a BNN where only 1-bit words and activations are needed [114], [115]. Originally used in FPGAs to take advantage of their configurability and offset the area and power overhead, BNNs have also been shown to work with RRAM in both simulation [116] and experiment [23]. When using a binary activation function, a 1-bit word-line driver and sense amplifier can be used rather than an ADC [117]. This design forgoes using multiple states in the device and avoids the additional circuit overhead. To activate many rows at a time, these networks can change the threshold of their sense amplifier to implement a binary activation function which quantizes all activations to 0 and 1. Although this implementation is appealing from a circuit perspective it suffers greatly when scaling the data sets to more complex problems [115]. Rastegari et al. [115] showed 9% performance degradation on ImageNet when going from full precision weights to binary weights. In addition to accuracy, BNNs struggle with training, as they are trained using full precision weights only to be quantized during inference.

SNNs have also been used to bypass the peripheral circuit overhead of ADCs [24]. Since SNNs only output spikes rather than conventional multibit digital values, an analog circuit can be used to integrate the current through PCM memory and fire a spike when it has passed a threshold. Though this technique is similar to BNNs, it makes use of the time domain by integrating over time and slowly reducing the state value of the neuron over time similar to the behavior of leaky-integrate and fire neuron model. Like the BNN, however, SNNs have issues with both accuracy and training preventing them from seeing large-scale use.

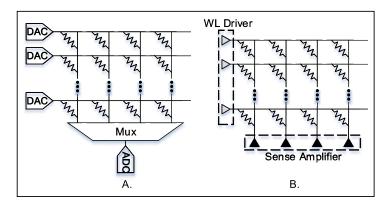

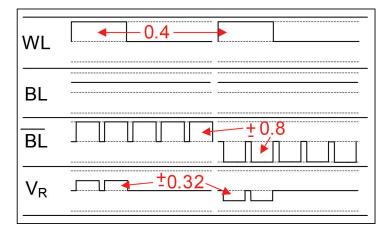

In Figure 10, we show both ends of the complexity spectrum ranging from DACs and ADCs to word-line drivers and sense amplifiers. In the past, many optimistic designs used multilevel inputs, high precision designs, and MLCs. However, such designs have proved to be difficult given cell-to-cell variance and select transistor source degradation. This gave rise to simpler designs using just word line drivers and sense amplifiers with single state cells, but as we discussed these designs have had difficulty in scaling to larger problems. As a result, most recent CIM designs utilize word-line drivers and ADCs [103]. This configuration is popular because it allows multiple rows to be read at the same time, and avoids the source degradation problem that occurs when using multilevel inputs.

#### Zero skipping

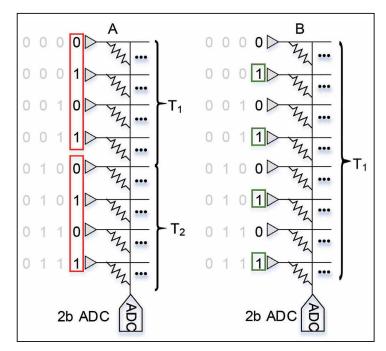

There are two common techniques for performing CIM. The first technique, which we refer to as *baseline*, is simply to read as many rows as the ADC precision allows (e.g., for a 3-bit ADC, we read eight rows simultaneously). The next technique is commonly called zero skipping [118]–[120], where only rows with "1"s are read. Zero-skipping performs faster than the baseline technique because for most cases it will process more total rows per cycle. In Figure 11, we provide an example case for zero-skipping where eight total rows are read using a 2-bit ADC. Baseline (11A) requires two cycles since it targets four consecutive rows at a time. Zero-skipping (11B) is able to finish all eight rows in a single cycle because we only consider the "1"s in the input vector.

There are few reasons not to perform zero skipping, unless there is limited input data bandwidth or the eNVM has high variance and accumulated too many errors. A recent work [120] has exploited this technique along with compression to achieve upward of 10× performance improvement. They illustrate that in most DNNs used today, activation sparsity is well above 50%. In fact, the larger the size of the neural network model the higher activation sparsity is observed.

#### Impact of variance in in-memory computing

At the device level, the fundamental performance bottleneck is a function of the device-to-device variance and the on-to-off ratio of each cell. These two properties define the number of distinguishable states that can be accurately read from a column

Figure 10. Two different peripheral circuit configurations for neural networks for compute in memory. (a) DACs and ADCs are used for multibit activations and reading higher precision. (b) 1-bit wordline drivers and sense amplifiers can be used to implement BNN and minimize area and power.

of the crossbar. If more states are read than can be accurately distinguished, then errors in the operation will occur following the distribution of the device-todevice variance. Since these errors compromise the

Figure 11. Simplified breakdown of ADC reads in baseline and zero-skipping with 2-bit ADC precision. (a) Baseline targets four consecutive rows at a time since the 2-bit ADCs are capable of distinguishing four states. (b) Zero skipping targets the next four rows where the word-line is enabled. This way we can read more rows and not overflow our ADC.

accuracy of the operation, the performance can no longer be compared to that of a bit-accurate CMOS implementation. Interestingly, in many data-intensive applications, particularly in neural networks, limited amounts of variance can be tolerated.

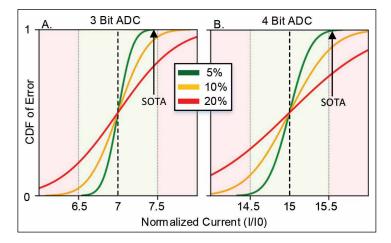

Modern eNVM technologies, such as PCRAM and RRAM, suffer considerably from device-to-device variance. State-of-the-art devices [36] have been demonstrated with a resistance standard deviation of 3.5%, on-to-off ratio of >10<sup>2</sup>, logic process and voltage compatibility, and high density. That said, analyses focused on solely device variability have revealed that the intrinsic and cell-to-cell variability can result in standard deviation that range from 5% to 50% depending on the write effort and the final stored resistance state [121], [122]. While lower nominal variability has been achieved in limited experimental research, real-world factors such as device drift and degeneration along with limited write-energy budget mean that well-controlled variance is rarely guaranteed and often practically impossible. The latter implies a precision/power tradeoff design-space that encourages algorithmic solutions to the variance issue.

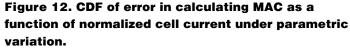

In Figure 12, we demonstrate how, given enough variance, a CIM operation will result in an error. We show three cases: 5%, 10%, and 20% variance in the resistance of the memory state. This figure depicts the resultant variance expressed as the cumulative distribution of the computing error, when seven on-state cells are being read (the maximum allowed by a 3-bit ADC) and when 15 on-state cells are read (the maximum for a 4-bit ADC). Recent work [123] has shown

several techniques on how the impact of device level variance can be reduced at the system level by controlling the operating speed based on the variance of the devices and importance of the particular operation. In 8-bit matrix multiplication, an error when computing the product of the most significant bits is 2<sup>14</sup> times more costly than an error for the least significant bits. Therefore, when operating on the most significant bit the number of rows being read should be reduced to minimize error at the system level.

## Implementation of neural networks

#### Vector operations in DNN accelerators

So far, we have discussed the various memory technologies and circuit design techniques to implement CIM engines. Despite matrix multiplication being the bulk of the workload, there are other essential operations to implement in a DNN accelerator. Fortunately, these operations represent a small portion of the workload since they operate directly on input and output vectors rather than performing matrix transformations on the data. There are several examples of this in CNNs, LSTMs [124], and transformer networks [125]. In all cases, these element-wise vector operations are performed post-matrix multiplication and thus have at least twice the bit-precision of the matrix operations.

In a CNN, the most common vector-wise operations are element-wise addition and comparison for bias and ReLU [126]. ReLU is particularly popular given that it typically yields the highest accuracy and also has the simplest operation. Other popular activation functions like sigmoid and tanh require exponential functions and division which require more complex CMOS logic. In low precision logic these can be implemented as lookup tables, however, in higher precision accelerators expensive ALUs are required. Many CNN accelerators [11] create special cores for processing these nonlinear activation functions and applying biases. A similar approach can be used for CIM accelerators, where eNVM arrays process the matrix operations and these vector operations are performed in special logic units.

For training deep CNNs, batch normalization [127] has become an integral component of all very DNNs. Prior to batch normalization and the use of residual [28] and dense [128] connections, very DNNs suffered from the vanishing and exploding gradient problems. Batch normalization normalizes the outputs of

intermediate layers and applies a bias and scaling parameter to each output. This adds additional complexity to the necessary ALU operations required because performing multiplication and division are more challenging than addition and comparison. However, this can be avoided in all inference-only accelerators since the normalization, bias, and scaling parameters can be folded together [129].

Another popular neural network architecture for extracting patterns in sequences and time is the RNN. The most popular form of the RNN is a long short-term memory (LSTM). eNVM is especially interesting for implementing LSTMs since they are constructed from large fully connected layers and thus have far more parameters and greater dependence on memory bandwidth. Recent work [130] has demonstrated an RRAM-based RNN accelerator. They create a special function unit (SFU) for the many vector operations of RNNs to complement the PE used for matrix multiplication. Although CMOS logic is used to implement the SFUs, the number of vector operations is far fewer than matrix operations, and therefore does not negate the performance benefit from using RRAM.

#### Weight and activation quantization

Neural networks are most commonly trained in high precision 32-bit floating point operations. Existing infrastructure in BLAS [131] and GPUs enabled sufficient performance. However, new research trends seek to use lower precision weights and activations to achieve the same results. Naturally, this has big implications in terms of memory capacity, data transport, and computation as the complexity of all three scales with the precision of the operands. Given the performance advantages, popular tools like TensorFlow and PyTorch have created packages dedicated to quantized arithmetic.

Originally, a "binarized" neural network [132] was shown to yield good results for small data sets. This network was trained with full precision weights, but during inference these weights could be stored as just 0 and 1. Later work has shown that this technique did not scale well to more challenging data sets [129], [133], [134], but lower precision weights and activations (8-bit) could still be used on large data sets like ImageNet [135]. There are different types of quantization, namely post training quantization and training aware quantization [129]. Post training quantization uses statistics from the weights and activations distributions to quantize a pretrained model. Training aware quantization trains a quantized model by quantizing full precision weights during the forward pass of backpropagation, and proceeding to train the model as if it were not quantized.

Most works in traditional CMOS accelerators [3] focus on 8-bit integer weights and activations for inference since it yields a nice balance between performance and accuracy. In [129] and [134], a small accuracy degradation can be observed when transitioning from full precision to 8-bit arithmetic. As the precision is lowered beyond 8 bits, a much larger accuracy degradation occurs. For training higher precision is often used [136], however, recent work has shown that it is possible to use 8-bit precision to train networks as well [136]–[138].

#### CIM array level simulators

eNVM have many new properties that make it difficult to determine their utility in creating machine learning accelerators. Of course it is better to have lower read energy and latency, but understanding how important these properties are at the system level is challenging. This problem is particularly important in device engineering so research effort is allocated to the most important device properties. For example, in the design of a system with low ADC precision (2-bit) device variance and on-to-off ratio have a much lower impact on accuracy and performance than a system with high precision ADCs. It is these types of scenarios that simulators seek to evaluate to both guide device level research and provide accurate power, performance, and area estimations for CIM system level designs.

The design and implementation of these simulators is a research challenge in itself. Typical circuit simulations like SPICE are notoriously slow for even small designs. At the same time, modeling all these properties while evaluating the memories in a higher level system is not only computationally demanding, but rarely explored until recently. Large neural networks are already extremely computationally demanding although they only perform matrix multiplications with optimized BLAS libraries on dedicated hardware. Simulating the same networks with circuit and device level components is even more computationally challenging. Several works [139]–[142] have made promising initial progress on this problem.

An early work, NVSim [139], was not developed specifically for DNNs. Since they avoid the computational complexity of a DNN accelerator, they are able to focus on lower level details that allow for a more

accurate comparison with flash for server workloads. More recent works [140]–[142] have extended the idea, but for evaluating DNNs. These simulators use object-oriented models of circuit components and devices to accurately model power, variance, delay, and other properties that must be modeled to give circuit level approximations.

Recent works, such as NeuroSim [140], explore the simulation tradeoff space choosing the important characteristics to model. Given the notoriously slow simulation time of accurate SPICE models, tradeoffs have to be made if a realistic DNN will be simulated. However, accurate estimations for area and power can be achieved by abstracting temporal variation and considering fixed energy and delay parameters for all array level components and global interconnects. RxNN [142] gives special attention to nonidealities of emerging devices and peripheral circuits as these will be fundamental performance bottlenecks in any realistic design. In both simulation tools, all devices from this article can be evaluated with both optimistic and pessimistic parameters. Power and performance breakdowns can be gathered across circuit level components to identify the largest sources of power to motivate and guide future research effort.

#### Network on chip for CIM accelerators

Although CIM seeks to minimize data transport, it is nonetheless an important aspect of implementing a CIM-based DNN accelerator. Fortunately, CIM-based architectures are similar to CMOS- and SRAM-based designs and thus make use existing research progress in network on chip (NoC), routers, and interconnects. Despite these similarities, there are some differences that require special attention. Given that CIM accelerators offer the advantage of high density and low power, low overhead NoC designs, such as those mentioned in [143], are of special interest. Furthermore, since CIM accelerators typically run at lower clock frequency and struggle with computational efficiency [103], special routing policies [144] will likely be required if eNVM CIM systems are to be used in real-time embedded systems.

Recent work [145] has proposed a new data flow based on prior work in CMOS-based CNN accelerators [5], [9]. This work implements a new weight mapping strategy for minimizing data movement in CIM DNN accelerators. As we discuss further in the "CIM-based accelerator architecture" section, eNVM PEs are not typically reprogrammed and hence each compute unit is not capable of performing each operation in a DNN. Therefore, the mapping of weights to compute units is a new challenge that was avoided in CMOS- and SRAMbased designs. Using this data flow and mapping strategy, the authors demonstrate improvements in power, performance, and memory efficiency.

Since all of the eNVM candidates are both process and voltage compatible with CMOS, we expect future research in interconnects to be coupled with CIM research. Emerging technology such as optical interconnects [146] or wireless NoCs [147] can be directly applied to CIM to further reduce the cost of data transport. Although these technologies need further research and development before mainstream adoption, they promise to reduce power and improve throughput over traditional interconnects, particularly for global routing layers. The combination of CIM and new interconnect technologies has the potential to drastically reduce power in DNN accelerators by both reducing the cost of data transport and eliminating a large fraction of the total data movement required.

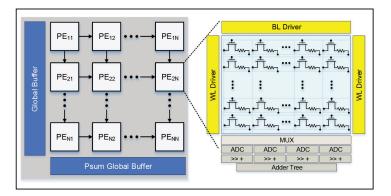

## CIM-based accelerator architecture

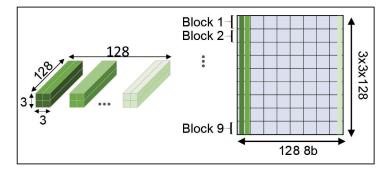

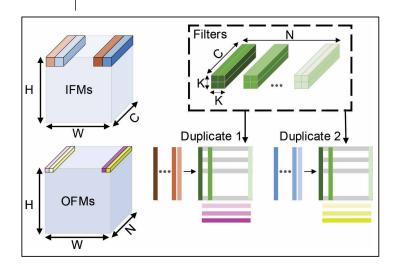

In previous sections, we describe the different components that go into creating a standalone CIM PE. By encapsulating the array, ADCs, and shift and add logic, a matrix multiplication engine can be created. Using these arrays as building blocks, prior work has implemented CNNs where a group of arrays implement a larger matrix multiplication. In Figure 13, we illustrate this idea, showing how a group of arrays is tiled together to form a PE and then used in a larger systolic array that can perform matrix operations. In most designs so far [103], [145], [148], the most common crossbar choice is  $128 \times 128$ where 8 bit weights and activations are used. Therefore, each array can perform a  $128 \times 16$  dot product on its own requiring only the 128-byte input vector. These arrays can easily be pieced together to form larger matrices. For example, a  $1024 \times 1024$  matrix can be formed by a  $8 \times 64$  grid of  $128 \times 128$  arrays.

This has important implications as modern DNNs such as CNNs and RNNs contain a workload of almost entirely matrix multiplication [101]. Despite performing more complex operations, the core operations of CNNs and RNNs are converted into matrix multiplication. In Figure 14, we further depict how these arrays can be pieced together to form a larger matrix that forms the kernel of a CNN. In this example, both input feature maps and filters are vectorized with the filters forming the columns of a matrix. The vectorized feature maps are input to the crossbar to perform matrix multiplication, where the results are output feature maps for this layer in a CNN.