# Double-Gate W-Doped Amorphous Indium Oxide Transistors for Monolithic 3D Capacitorless Gain Cell eDRAM

H. Ye<sup>1\*</sup>, J. Gomez<sup>1\*</sup>, W. Chakraborty<sup>1</sup>, S. Spetalnick<sup>2</sup>, S. Dutta<sup>1</sup>, K. Ni<sup>3</sup>, A. Raychowdhury<sup>2</sup>, and S. Datta<sup>1</sup>

<sup>1</sup>University of Notre Dame, Notre Dame, IN 46545, USA; <sup>2</sup>Georgia Institute of Technology, Atlanta, GA 30332, USA;

<sup>3</sup>Rochester Institute of Technology, Rochester, NY 12623 USA

\*Equal Contribution; Email: hye1@nd.edu

Abstract—We experimentally demonstrate W-doped amorphous In<sub>2</sub>O<sub>3</sub> double-gate field-effect transistors (DG IWO FET) with 5nm channel thickness and 50nm channel length exhibiting (a) excellent subthreshold slope (SS) of 73mV/dec, (b) record  $I_{D SAT}$  of 550µA/µm at  $V_{GS}$ - $V_{TH}$ =2V,  $V_{DS}$ =1V, and (c) high on-off ratio>  $1 \times 10^{12}$ . 20nm gate length IWO DG FET was also fabricated to demonstrate scaling potential. We experimentally demonstrate IWO FET based capacitorless 2T gain cell embedded DRAM (eDRAM) ideal for monolithic 3D (M3D) integration exhibiting (a) cell level leakage current of  $\sim 1 \times 10^{-15} \text{A}/\mu\text{m}$  and  $\sim 1 \times 10^{-14} \text{ A}/\mu\text{m}$  at 25C and 85C, (b) retention time 1s and 300ms at 25C and 85C respectively with effective storage node capacitance of 1 fF. Array level analysis of IWO capacitorless 2T eDRAM shows that access time < 2ns is achievable with further scaling and moderate outside-the-rail voltages. M3D 2T eDRAM based on IWO FETs offers lower write time than embedded non-volatile random access memory (eNVRAM) and consumes 100x lower stand-by power and 1000x lower refresh power than conventional SRAM and eDRAM, respectively, making it an excellent candidate for fast and embedded memory with unlimited endurance.

## I. INTRODUCTION

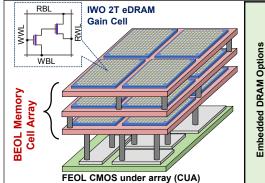

Recent years have witnessed a rise in domain specific accelerators designed for graphics, deep learning, bioinformatics, image processing and other tasks [1-4]. In addition to the obvious benefit of specialization of logic cores and high level of parallelism, a key source of the acceleration comes from availability of local memories for individual cores and large shared buffer memory on a monolithic chip. Accelerators have created an increasing need of high-density, highperformance, low stand-by power memory alternatives to traditional SRAM. Capacitor-less two-transistor gain cell embedded DRAM is a promising candidate due to its potential for higher density, lower power consumption, higher endurance than eNVRAM, 2-port functionality, non-ratioed circuit operation and their scaling potential to advanced nodes. Gain cells are dynamic memory cells made of two logic transistors, where the second transistor is used not only to increase the incell storage capacitance but also to amplify the readout charge via the transconductance gain resulting in a non-destructive read. In this work, we fabricate BEOL compatible W-doped Indium Oxide (In<sub>2</sub>O<sub>3</sub>) FETs with ultra-low leakage of 1fA/um to demonstrate a monolithic 3D capacitor-less 2T gain cell eDRAM (Fig. 1). Compared to existing 2T eDRAM [6] in Fig. 2, the fabricated M3D IWO 2T eDRAM shows 1000x higher retention time, comparable access time of 1-10ns and 1000x lower refresh power. Finally, we perform a design-space

optimization of the prototype M3D IWO 2T eDRAM to determine its potential for high-speed, high-density and low power embedded memory applications.

## II. DEVICE FABRICATION

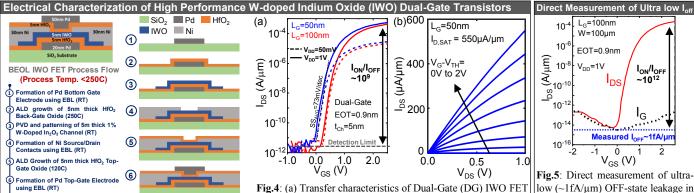

The low-thermal budget (<250C) process flow and schematic structure of the fabricated tungsten (W)-doped amorphous  $In_2O_3$  (IWO) FET with 5nm ALD HfO<sub>2</sub> gate oxide is shown in Fig. 3. First, 20nm thick palladium (Pd) metal gate was deposited via e-beam evaporation and liftoff as back-gate followed by 5nm-HfO<sub>2</sub> back gate oxide deposition using thermal ALD at 250°C. Next, 5-nm amorphous W-doped (1 wt. %)  $In_2O_3$  channel was deposited by RF magnetron sputtering in the presence of 0.02 Pa excess O<sub>2</sub> at room temperature. 30nm thick Ni was deposited as the source and drain electrode followed by 10-min anneal at 150°C under N<sub>2</sub> to improve the contact resistance. Finally, 5nm thick HfO<sub>2</sub> top gate oxide was deposited using thermal ALD at 120°C, followed by deposition and patterning of Pd as the top gate.

## **III. IWO FET CHARACTERIZATION**

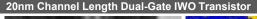

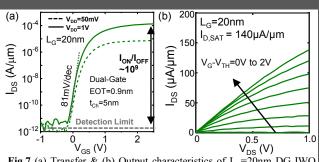

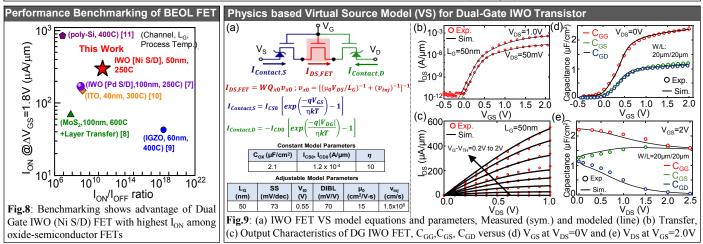

Fig. 4 (a) shows the measured transfer characteristics of 50nm and 100nm channel length (L<sub>G</sub>) IWO Double Gate (DG) FETs displaying SSAVG of 73 mV/dec and 68 mV/dec respectively, under V<sub>DS</sub> 1V. Output characteristics of the DG IWO FET with  $L_G=50nm$ , shown in Fig. 4 (b), exhibit a high saturation current of 550  $\mu$ A/ $\mu$ m at V<sub>GS</sub>-V<sub>TH</sub>=2V and V<sub>DS</sub>=1V, thanks to the low contact resistance between IWO film and Ni electrodes. As the off-state leakage current of the IWO FET is extremely low [7], instrumentation with the current detection limit at approximately 10<sup>-13</sup>A cannot directly measure the I<sub>OFF</sub> leakage. Hence, an ultra-wide device (W=100µm) was used to directly measure the off-state leakage of  $\sim 1 \times 10^{-15}$  A/µm in DG IWO FET, as shown in Fig. 5, resulting in high I<sub>ON</sub>/ I<sub>OFF</sub> ratio of 1x10<sup>12</sup>. I<sub>OFF</sub> was found to be limited by the gate-to-drain leakage and can be reduced by increasing the effective oxide thickness (EOT). Figs. 6(a,b) show the cross-sectional TEM image and STEM mode EDX profile respectively, of fabricated IWO FET with  $L_G = 20$  nm. Fig. 7(a, b) show the measured transfer and output characteristics, respectively, of L<sub>G</sub>=20nm DG IWO FET exhibiting well-tempered electrostatics with SS<sub>AVG</sub> of 81mV/dec. The performance of L<sub>G</sub>=50nm DG IWO FET was benchmarked against other BEOL compatible FETs (Fig. 8), where  $I_{ON}$  is taken at  $V_{DS}=1V$ over a 1.8V V<sub>GS</sub> swing from the reported I<sub>MIN</sub> point. DG IWO FETs in this work display the highest I<sub>ON</sub> over a fixed swing, maintaining excellent I<sub>ON</sub>/I<sub>OFF</sub> ratio of 1x10<sup>12</sup> compared to other BEOL compatible FETs. Hence, IWO DG FET is an

28.3.1

Authorized licensed use limited to: Georgia Institute of Technology. Downloaded on June 28,2021 at 12:33:48 UTC from IEEE Xplore. Restrictions apply.

excellent candidate for M3D capacitor-less 2T eDRAM application.

#### IV. VIRTUAL SOURCE MODEL FOR IWO FET

We extend the semi-empirical physics-based Virtual Source (VS) model for IWO transistors [12]. We incorporate gatevoltage (V<sub>GS</sub>) modulated Schottky diodes in series with an intrinsic FET to capture the VGS dependent source-drain contact resistance in IWO FET [7]. According to the VS model, the intrinsic FET drain-to-source current ( $I_{DS, FET}$ ) is computed as the product of the mobile charge density  $(Q_{inv})$ and injection velocity  $(v_{x0})$  as:  $I_{DS, FET} = WQ_{inv}v_{x0}$ , where W is the geometric device width. The current through source-drain Schottky junction ( $I_{CS}$   $I_{CD}$  respectively) is empirically modeled as shown in Fig. 8(a). Current continuity equation for the gated Schottky source-drain contacts and the intrinsic IWO FET is solved iteratively to match the experimental transfer (Fig. 8(b)) and output characteristics (Fig. 8(c)). The model parameters are listed in Fig. 8(a). The voltage-dependent capacitances are estimated from the derivative of the terminal charges with respect to the terminal voltages, following channel-charge partitioning as [12]. Fig. 8(d) shows that the VS charge model captures the V<sub>GS</sub> dependence of gate-to-channel capacitance  $(C_{GG})$ , gate-to-source capacitance  $(C_{GS})$  and gate-to-drain capacitance ( $C_{GD}$ ) at  $V_{DS}=0V$ . Fig. 8(e) shows excellent agreement between measured and simulated  $C_{GG}$ ,  $C_{GS}$ ,  $C_{GD}$ characteristics with varying V<sub>DS</sub>.

#### V. CHARACTERIZATION OF IWO CAPACITORLESS 2T EDRAM CELL

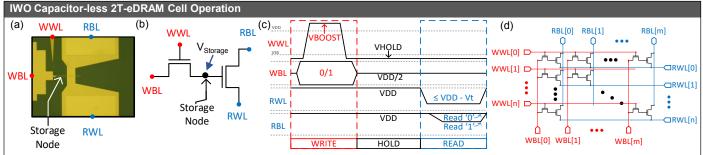

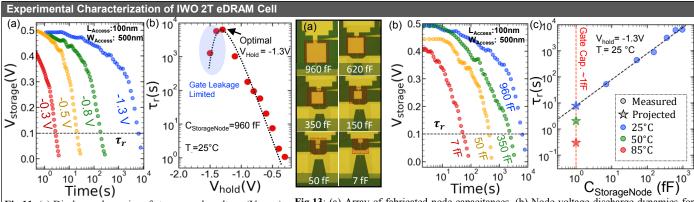

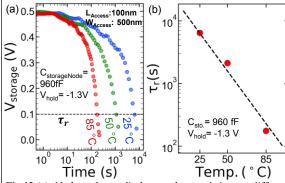

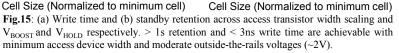

Fig. 10 (a) shows an optical image of the fabricated capacitor-less IWO 2T DRAM gain cell with four signal lines: read-bitline (RBL), write-bitline (WBL), write-wordline (WWL) and read-wordline (RWL), along with the corresponding circuit schematic shown in Fig. 10(b). The state of the memory cell is given by the stored charge in the gate capacitance of the read transistor. Fig. 10 (c) illustrates the cell bias conditions used during the write, read, and hold modes. Write time and retention time are improved by holding WWL at V<sub>BOOST</sub>, above V<sub>DD</sub>, and V<sub>HOLD</sub>, below V<sub>SS</sub>, during write and hold phases respectively. Fig 10 (d) shows how the cell is integrated into an eDRAM array. We characterize the performance of the IWO eDRAM cell, particularly during the hold operation in which the storage node is discharged over time. A characteristic retention time  $(\tau_r)$  is extracted when the node has discharged 80% of the total charge. We track the voltage of the storage node by continuously measuring the drain current of the read transistor. The storage node voltage (Vstorage) can be obtained from the  $I_d$ -V<sub>g</sub> of the read transistor. Fig. 11 (a) shows the measured discharge dynamics of the eDRAM cell for different hold voltages. By plotting the characteristic retention time for each hold voltage (Fig. 11 (b)), an optimal hold voltage (V<sub>HOLD</sub>) is extracted at which max retention is achieved before it is reduced by gate leakage. At the optimal  $V_{HOLD}$  we study the impact of varying temperature on  $\tau_r$  for three different temperatures: 25°C, 50°C and 85°C. The discharge dynamics are shown in Fig. 12 (a). Fig. 12 (b) shows the dependence of  $\tau_r$ on temperature. Fig. 13 (a) shows the optical images of various

eDRAM cells with different node capacitances that range from 960 fF to 7fF. While the fabricated capacitor-less IWO eDRAM cell has the lowest node capacitance of 7fF, we project it to be  $\sim$ 1fF at a further scaled geometry. Figs. 12 (b, c) show the discharge dynamics for different in-cell node capacitances and the retention time as a function of node capacitance, respectively. Extrapolating these results, retention time for 1fF node capacitance at 25°C was found to be  $\sim$ 10s. Projected retention time at 50°C and 85°C are 2s and 0.3sec, respectively.

#### VI. IWO 2T EDRAM ARRAY

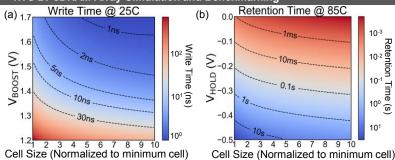

For array level simulation of IWO 2T eDRAM, we use a resistivecapacitive (RC) delay model considering a 128x128 eDRAM array. Interconnect resistance, peripheral (BL/WL driver) output resistance and memory cell transistor channel resistance are treated separately, with a series of cells in a row or column forming a distributed RC line. To compute the read, write, and retention times the large-signal channel resistance of the pertinent transistor, calibrated to the projected transistor (reduced contact resistance and V<sub>TH</sub> engineered), is estimated at the bias points defined by the midpoints of successive voltage segments. The total time-delay is the sum of the delay for the segments covering the voltage slew range and the limiting interconnect delay time in the case of read and write. The write and retention timing results across a range of V<sub>BOOST</sub> and V<sub>HOLD</sub>, as shown in Fig. 15, shows <1ns write time with >1s retention are feasible within compact cell dimensions and moderate outside-the-rails voltages. Fig. 16 shows that these timing results describe a class of memory that is much faster ( $\sim 10x$ ) than emerging nonvolatile memories (eNVM) while requiring significantly less (~100x) standby power than conventional SRAM and eDRAM [18-20]. Fig. 16 (b) shows, an array density scaling path through 3D stacking of BEOL memory layers, where cost-effectiveness and density eventually saturate with increasing no. of stacking layers. For these plots, we conceive of a 10% compounding increase in cost while requiring that the equivalent peripheral area at 60% efficiency be present in the scaled CMOS logic layer [21]. Benchmarking against other memory technologies (Fig. 17) the IWO FET based M3D capacitor-less 2T eDRAM emerges as a promising alternative to fill the gap between eNVM and traditional Si SRAM and eDRAM

#### **VII.** CONCLUSIONS

We fabricated and characterized BEOL compatible Wdoped amorphous  $In_2O_3$  (IWO) FETs with record  $I_{ON}$ (550µA/µm), ultra-low leakage (~1fA/µm) and scaled  $L_G$ (20nm). Using IWO FETs we fabricated capacitorless 2T DRAM cell with high retention time and low refresh power, which bridges the gap between eNVRAM and traditional SRAM, eDRAM.

**References:** [1] Z.Jia et. al., arXiv:1903.07486 (2019), [2] S.Han et. al., ISCA'16, [3] Y.Turakhia et. al., ASPLOS'18, [4] W.Qadeer et. al., ACM'13, [5] A. Lilak et. al, US20200227416, (2020), [6] K. C. Chun et. al., VLSI '10, [7] W. Chakraborty et. al., VLSI'20, [8] Q.Smets et. al, IEDM'19, [9] H. Kunitake et. al, IEDM'18, [10] S.Li et. al., Nat. Mat.'19, [11] Fu-Kuo Hsueh et. al, IEDM'19, [12] L.Wei et. al., TED (2012), [13] M. Oota et. al., IEDM '19, [14] M. Meterelliyozl et. al., IEDM'14, [15] J.Y. Wu et. al., IEDM'18, [16] K. Rho et. al., ISSCC'17, [17] R. Giterman et. al., ISSC'20, [18] K. Chul et. Al, JSSC'11, [19] N. Planes et. al., VLSI'10, [20] S. Natarajan et. al., IEDM'14, [21] N. Ramaswamy, IEDM'17 Short Course

Acknowledgment: This work was supported in part by ASCENT, one of six centers in JUMP, sponsored by DARPA and the Semiconductor Research Corporation (SRC).

## BEOL Compatible W-doped Indium Oxide Transistors for 2T eDRAM with Peripheral CMOS Under Array

|                              |                                                                                                              |                                                                                                                                                                                    | tors for 21 eDRAW with Fempheral CWOS onder Array                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |  |  |  |  |

|------------------------------|--------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| Туре                         | 1T-1C [5]                                                                                                    | 2T [6]                                                                                                                                                                             | IWO 2T [This Work]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| rcuit Schematic              | Si Channel.                                                                                                  | Si Channel.                                                                                                                                                                        | WO Channel.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |  |  |  |  |

| etention Time                | 100-2000 μs                                                                                                  | 100-1000 μs                                                                                                                                                                        | 1-10 s                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Access Time                  | 1-10 ns                                                                                                      | 1-10 ns                                                                                                                                                                            | 1-10 ns                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |  |  |  |  |

| estructive Read              | Yes                                                                                                          | No                                                                                                                                                                                 | No                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |  |  |  |  |

| ensity (Mb/mm <sup>2</sup> ) | 10-30                                                                                                        | 1-10                                                                                                                                                                               | 80-200                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |  |  |  |

| Periphery                    | FEOL                                                                                                         | FEOL                                                                                                                                                                               | FEOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

| Bit Cell                     | FEOL/BEOL                                                                                                    | FEOL                                                                                                                                                                               | BEOL                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |  |  |  |  |  |

|                              | cuit Schematic<br>etention Time<br>Access Time<br>structive Read<br>nsity (Mb/mm <sup>2</sup> )<br>Periphery | cuit Schematic Si Channel BEOL<br>Si Channel Cap.<br>etention Time 100-2000 µs<br>Access Time 1-10 ns<br>structive Read Yes<br>nsity (Mb/mm <sup>2</sup> ) 10-30<br>Periphery FEOL | cuit Schematic Image: Channel Image: Cap. Si Channel Image: Si Channel |  |  |  |  |  |  |  |  |  |

**Fig.1:** Monolithic-3D integration of Tungsten-doped Indium Oxide (IWO) channel FET based 2T-eDRAM allows high memory density, high retention time, ultra-low refresh power and >90% cell-availability

**Fig.2:** Comparison of different embedded DRAM options demonstrating IWO 2T DRAM to exhibit the desired characteristics of high retention time and low access time due to its high  $I_{on}/I_{off}$  ratio. The BEOL compatibility allows high density and the 2T topology allows a non-destructive read

IWO FET with L<sub>G</sub>=50nm

with L<sub>G</sub>=100nm and 50nm (b) Output characteristics of DG

**Fig.3**: Schematic device structure and process flow of <u>Dual-Gate BEOL IWO FET</u>

ultra-wide DG IWO FET showing

I<sub>OFF</sub> limited by gate-current (I<sub>G</sub>)

Fig.6 (a) Cross-sectional TEM image and (b) STEM-EDX elemental map showing fabricated structure of ultra-scaled Dual Gate IWO FET with  $L_G=20nm$

**Fig.7** (a) Transfer & (b) Output characteristics of  $L_G=20nm$  DG IWO FET with well tempered electrostatics, showing  $I_{D,SAT}$  limited by contact resistance (~1k $\Omega$ -µm)

28.3.3

**Fig.10**: (a) Optical image and (b) corresponding circuit schematic of capacitor-less 2T-eDRAM, (c) timing diagram showing voltage waveforms for Write, Hold, and Read operations, including  $V_{BOOST}$  (above VDD) and  $V_{HOLD}$  (below VSS) and (d) schematic of the eDRAM array with individual cells.

**Fig.11**: (a) Discharge dynamics of storage node voltage ( $V_{Storage}$ ) at different hold voltages ( $V_{Hold}$ ) and (b) dependence of retention time ( $\tau_r$ ) on different  $V_{Hold}$

**Fig.12**:(a) Node voltage discharge characteristics at different temperatures and (b) dependence of retention time on operating temperature

| (a)                                                                                                                                                                                   | (b)100<br>(n : 80<br>e)                                             | eDRAM Type                    | 2T [13]         | 1T-1C<br>[13]   | 1T-1C<br>[14] | 2T [6] | This<br>Work    |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|-------------------------------|-----------------|-----------------|---------------|--------|-----------------|--|--|

| 10 <sup>2</sup> ■ PCM 40nm[15] <b>ENVM</b>                                                                                                                                            |                                                                     | V <sub>DD</sub> (V)           | 1.2             | 1.2             | 1.05          | 1.2    | 1.0             |  |  |

| € IGZO NOSRAM [13]                                                                                                                                                                    | ts 60<br>3 40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40<br>40 | <sup>1</sup> Density (Mb/mm²) | 80              | 80              | 17.5          | 4      | 180             |  |  |

| WO 2T eDRAM<br>(This Work) 3T eDRAM [17]                                                                                                                                              | 80%                                                                 | BEOL Compatible               | Yes             | Yes             | No            | No     | Yes             |  |  |

| S C This Work 3T EDRAM 16nm<br>[18] ●<br>3T EDRAM 65nm<br>3T EDRAM 65nm<br>[19] ■                                                                                                     | Ĕ160                                                                | Cell Cap. (fF/cell)           | 1.2             | 3.5             | 13.8          | *      | 1               |  |  |

| SRAM 28nm FDSOI                                                                                                                                                                       | ₹ 120<br>≥ 80 Stack Efficiency.                                     | Retention(ms@85°C)            | 10 <sup>7</sup> | 10 <sup>8</sup> | 0.3           | 1      | 10 <sup>3</sup> |  |  |

| 10 <sup>-1</sup> 10 <sup>-1</sup> 10 <sup>0</sup> 10 <sup>1</sup> 10 <sup>2</sup>                                                                                                     | 1 80<br>40 → 60%<br>→ 70%<br>→ 80%                                  | <sup>2</sup> Access Time (ns) | 30              | 30              | 5             | 1.6    | 3               |  |  |

| 0 10 <sup>-1</sup> 10 <sup>0</sup> 10 <sup>1</sup> 10 <sup>2</sup><br>Stand-by Power (μW/Mb)                                                                                          | 1 3 5 7 9 11 13<br># of Layers Stacked                              | Destructive Read              | No              | Yes             | Yes           | No     | No              |  |  |

| <b>Fig.16</b> : (a) Comparison of embedded storage technologies' timing and <b>Fig.17</b> : Monolithic-3D capacitorless 2T eDRAM based on W-doped In <sub>2</sub> O <sub>3</sub> FETs |                                                                     |                               |                 |                 |               |        |                 |  |  |

Fig.16: (a) Comparison of embedded storage technologies' timing and Fig.17: Wolfornine'sD capacitorities 21 CDKAM based on w-doped  $II_2O_3$  TETS standby power performance and (b) demonstrating projected density and cost scalability as the number of eDRAM layers increases.

28.3.4

Authorized licensed use limited to: Georgia Institute of Technology. Downloaded on June 28,2021 at 12:33:48 UTC from IEEE Xplore. Restrictions apply.