# A 90.4% Peak Efficiency 48V/1V Three-Level Hybrid Dickson Converter with Gradient Descent Run-Time Optimizer and GaN/Si Hybrid Conversion

Minxiang Gong<sup>1</sup>, Xin Zhang<sup>2</sup>, Arijit Raychowdhury<sup>1</sup> <sup>1</sup>Georgia Institute of Technology, <sup>2</sup>IBM T. J. Watson Research Center

Abstract

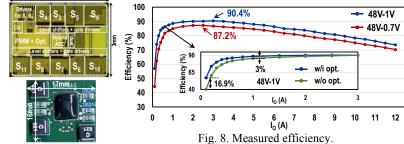

This work presents a 48V/1V DC-DC Point-of-Load (POL) converter for efficient high voltage conversion in data centers. The converter includes (1) a three-level hybrid Dickson topology with GaN/Si hybrid conversion achieving efficient flying capacitor (C<sub>F</sub>) utilization. (2) A gradient descent run-time optimizer finding optimal switching frequency (fsw) and number of fingers turned on (N<sub>F</sub>) during converter's operation. (3) A 10bit hybrid ADC for current sensing. The test chip is fabricated in 0.18µm BCD process and shows a 90.4% peak efficiency at 48V-1V conversion with a 240 A/inch<sup>3</sup> current density.

## **Introduction and Motivation**

Data centers are moving to the 48V power bus from conventional 12V. Therefore, direct 48V-to-1V point of load (POL) converters become popular. Recently, hybrid topologies [1]-[5] gain interest, which overcome high voltage stress and small duty ratio in the half bridge topology. However, first, prior works adopt N-1 C<sub>F</sub> to reduce max voltage on the switching node (V<sub>SW</sub>) N times, which increases component count and hursts the power density. Second, recent works only focus on the peak efficiency and ignore the operation range of load current (I<sub>O</sub>). This work proposes a threelevel hybrid Dickson converter achieving efficient utilization of both power switches and C<sub>F</sub> with a run-time gradient descent optimizer for efficiency enhancement across a wide range of I<sub>0</sub>.

Three-Level Hybrid Dickson Topology

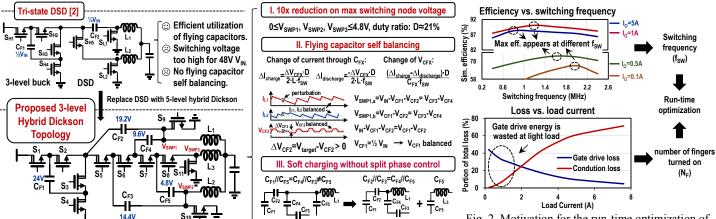

Recent work [2] proposes a tri-state double step-down topology achieving efficient C<sub>F</sub> utilization shown in Fig. 1. However, the max switching node voltage ( ${}^{1}\!\!/_{4}V_{IN}$ ) is not well-suited for 48V input, and a flying capacitor voltage ( $V_{CF}$ ) rebalancing technique is required. Inspired by [2], this work proposes a three-level hybrid Dickson topology (Fig. 1). By replacing the DSD topology with a five-level hybrid Dickson topology, the proposed topology has following features: (1) it reduces max V<sub>SW</sub> 10x and extends the duty ratio 10x with only five C<sub>F</sub> and 11 switches – a 54% and 21% reduction compared to [5]. (2) it has inherent  $V_{CF}$  balancing which eliminates additional controls. CF2-CF5 are balanced by inductors as described in [1],[2] and [4].  $C_{F1}$  is balanced by  $C_{F2}$ - $C_{F4}$  as shown by equations in Fig. 1. (3) To avoid  $C_F$  hard charging in Dickson structure, an additional inductor  $L_3$  is used to split  $C_{F5}$  out from  $L_1$ [6] for soft charging. The L<sub>3</sub> enables three phase operation which reduces output voltage (V<sub>0</sub>) ripple and support higher I<sub>0</sub>. Fig. 2 shows our analysis on efficiency versus frequency and gate drive loss, necessitating the run-time optimizer. First, the max efficiency occurs at different f<sub>SW</sub>. Second, when I<sub>O</sub> is low, the conduction loss (P<sub>C</sub>) is less than 12% of the total loss. Turning on all fingers of Si switches wastes large amount of drive power (10s of mW) and has limited P<sub>C</sub> reduction. Therefore, a run-time optimizer of f<sub>SW</sub> and

System Architecture and Circuit Implementation

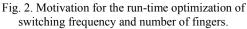

Fig. 3 shows the proposed converter system architecture, and the colored area indicates the die. The converter uses two off-chip GaN switches (S<sub>1</sub>, S<sub>2</sub>), nine on-chip Si LDMOS (S<sub>3</sub>-S<sub>11</sub>), forming a hybrid conversion [5]. Drive signals are generated from a 12bit digital PWM with a resolution of 156ps. S<sub>1</sub>-S<sub>3</sub>, and S<sub>5</sub>-S<sub>8</sub> require high voltage level shifters to accomplish high voltage gate driving. To have a precise power loss estimation, a 10bit hybrid ADC with a differential amplifier is proposed for sensing L<sub>1</sub>'s average current (I<sub>L1</sub>) when S<sub>1</sub> is turned on. The 10bit current information along with the 12bit on-time (ton) are sent to a gradient descent run-time optimizer. The optimizer calculates the power loss at each step and compares them to find the optimal f<sub>SW</sub> and N<sub>F</sub>. The f<sub>SW</sub> is controlled by a frequency divider capable for 4bit frequency tuning (0.52-4.4MHz). The 9x3bit  $N_F$  of  $S_3$ - $S_{11}$  are sent to finger scalable gate drivers for driving Si switches. The output voltage is quantized by a 6bit SAR ADC and a digital PID controller is

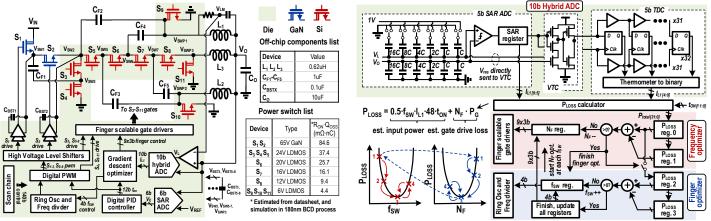

responsible for  $V_{\rm O}$  regulation. The circuit schematic of 10bit hybrid ADC and block diagram of the gradient descent run-time optimizer are shown in Fig. 4. The V<sub>L</sub> and V<sub>O</sub> indicating I<sub>L1</sub> are first converted by a 5bit SAR ADC. Then, the residual voltages on capacitors of the SAR ADC are directly sent to tail transistors of two voltage-to-time converters (VTC). Since the difference of residual voltages are small (<62.5mV), the VTC shows good linearity within such small input range. The difference between residual voltages is converted by a 5bit time-to-digital converter (TDC). Compared to conventional pipeline ADC, the proposed design eliminates intermediate amplifiers by reusing voltages on capacitors, which reduces area/power overhead. The 10bit IL1 is sent to a power loss calculator to estimate the power loss (P<sub>LOSS</sub>). The equation of P<sub>LOSS</sub> is shown in Fig. 4. Besides I<sub>L1</sub>, t<sub>ON</sub> also provides information of input power (P<sub>IN</sub>), which overcomes noise in the current sensing circuit. To optimize both f<sub>SW</sub> and N<sub>F</sub>, an iterative gradient descent method is used. The f<sub>SW</sub> optimizer performs gradient descent starting from the lowest f<sub>SW</sub> and stops at each step waiting for N<sub>F</sub> optimizer to find the optimal N<sub>F</sub>. Starting from the highest N<sub>F</sub> that all fingers are turned on, the N<sub>F</sub> is subtracted each time until its gradient becomes positive. Then, N<sub>F</sub>, and P<sub>LOSS</sub> are sent to f<sub>SW</sub> optimizer for remaining process. At each step of f<sub>SW</sub> or N<sub>F</sub>, the hybrid ADC starts conversion after PID controller is stabilized to ensure accurate IL1 sensing. Thus, the run-time optimizer finds the global minimum for both f<sub>SW</sub> and N<sub>F</sub> without interoperating converter's operation. Conventional level shifters face challenges of speed and reliability in high conditions. The proposed high-speed digital-assisted level shifter is shown in Fig. 5. It uses diode clamping for fast transition and current mirrors for symmetric pull-up/pull-down time. However, first, during the transition,  $I_{X-C}$  and  $I_{Y-C}$  copied from  $I_X$  and  $I_Y$  by current mirrors charge  $V_P$  and  $V_N$  to high. Second, in steady state, small currents  $I_{X-S}$  and  $I_{Y-S}$  discharge  $V_P$  and  $V_N$  gradually. To avoid output flipping, a digital logic is used to lock the output. Compared to conventional cascoded level shifter, it shows high speed (~1ns) with a smaller area  $(195 \times 65 \mu m^2)$ .

### **Measurement Results**

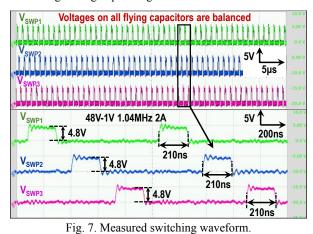

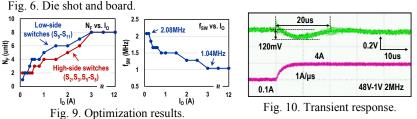

The test chip is fabricated in 0.18µm BCD process with an area of 4x3mm<sup>2</sup> (Fig. 6). Fig. 7 shows measured switching node waveform. The switching node voltages trip between 0V-4.8V, validating the proposed topology. In the large timescale, switching node voltages are stable indicating voltages on all flying capacitors are balanced. Measured efficiency is shown in Fig. 8. This work achieves 90.4% and 87.2% peak efficiency at 48V-1V and 48V-0.7V, respectively. The small figure in Fig. 8 shows efficiency improvement with proposed run-time optimizer. Fig. 9 shows N<sub>F</sub> and f<sub>SW</sub> at different I<sub>O</sub>. At low I<sub>O</sub>, switches are soft switched (with fixed dead-time) so  $f_{SW}$  is increased to reduce excessive ripple current ( $I_{ripple}$ ) on inductors. As Io increases, N<sub>F</sub> becomes larger for reduced P<sub>C</sub> while f<sub>SW</sub> is reduced for lower switching losses (P<sub>SW</sub>). Measured transient response is shown in Fig. 10. A 120mV voltage droop and 20µs response time is measured at a load step of 1A/µs. Fig. 11 shows measured current sensor accuracy with proposed hybrid ADC. The ideal resolution is 2mA, and the average error is within 9. Table I shows the comparison with state-of-the-art.

#### Acknowledgement

This project was supported by the Semiconductor Research Corporation (SRC) under grant JUMP ASCENT task ID 2776.033 and Intel Custom Funding.

#### References

- [1] R. Das, et. al., APEC, pp. 1997-2001, 2019.

- [2] K. Wei, et. al., ISSCC, pp. 190-191, 2020.

- [3] M. Choi, et. al., ISSCC, pp. 296-297, 2020.

- [4] D. Yan, et. al., JSSC, vol. 55, no. 4, pp. 988–998, 2020.

- [5] X. Yang, et. al., ISSCC, pp. 466-467, 2021.

- [6] R. Das, et.al., APEC, pp. 25-29, 2019.

Additional phase L<sub>3</sub> split out C<sub>F5</sub>

Fig. 1. Proposed three-level hybrid Dickson topology and features.

Fig. 3. Converter system architecture with on-chip Si device, off-chip GaN, digital regulation loop and run-time gradient descent optimizer.

Fig. 4. Diagram of 10bit hybrid ADC and run-time optimization of  $f_{\text{SW}}$  and N<sub>F</sub> with iterative gradient descent.

3-level buck

**Hybrid Dickson**

Fig. 5. High-speed digital-assisted level shifter.

Measured Avg error Avg error: 900 800 0 0.1 0.2 0.3 0.4 0.5 0.6 0.7 I<sub>1.1</sub> (A) 0.7 0.8 0.9 1 1.1 1.2 1.3 I<sub>1.1</sub> (A) 1.3 1.4 1.5 1.6 1.7 1.8 1.9 2 I<sub>L1</sub> (A)

Fig. 11. Current sensing results.

ළි<sub>200</sub>

A 100

APEC 2019 [1] ISSCC 2020 [3] SSCC 2020 [2] ISSC 2020 [4] SSCC 2021 I5 This work 180nm BCD 180nm BCD 180nm BCD 180nm BCD Technology 180nm BCD Discrete -state Doubl Double Step 12-level 3-level-3-level hybrid Topology Aulti-inductor hybr Step Down current doubler Down ries-capacito Dickson Input Voltage 48V 12V/24V 48-60V 48V 36-60V 48V 0.7-1V Output Voltage 0.5-1V Max Load Current 100A 3A 60A 1.5A 12A On-chip Si & GaN On-chip Si Ext. Si GaN n-chip Si & GAN Power Switches GAN Inductor 4x1uH 2x0.56uH 2x0.33uH+transforme 2x0.9uH 3x0.62uH #. of Flying Capacito 12x Voltage Reduction 4x 4x 16x 10x #. of External Switch 90.9%@48-1V, 88.3%@24-1V 92.8%@48-1V, 85.4%@48-1V 90.2%@48-1V 90.4%@48-1V 333kHz 2.5MHz 1MHz 333kHz 100kHz 100kHz

\*current density for component area only. #without Co and Cast-Table. I. Comparison with state-of-the-art.

No

On-chip Optimizati

**Current Density**