The overall research goal in ICSRL is to comprehend the mathematical and physical models that govern nature and our interactions with it. Engineering, has always been the application of man’s understanding of natural sciences to design systems that enable a better tomorrow. In our lab, we endeavor to explore such models of information processing and computation, as well as to design hardware solutions to physically realize them.

Algorithm-Hardware Co-Design for Efficient and Reliable Autonomous Machines

Autonomous machines (e.g., drones, robots, self-driving cars, AR/VR) need to operate efficiently, intelligently, and robustly. We conduct algorithm-architecture-circuit co-optimization for next-generation autonomous navigation, neuromorphic computing, and bio-inspired applications. We explore the reliability of safe-critical autonomous systems and propose cost-effective schemes to enable autonomy robustness. We build hardware accelerators for efficient perception, localization, planning and end-to-end learning of autonomous systems.

Key Publications: [CICC 2022][DATE 2022][DAC 2021][CAS-M 2021][JETCAS 2019][PEDRA]

Energy-efficient Hardware for Autonomous Systems, Machine Learning and Smart Sensing

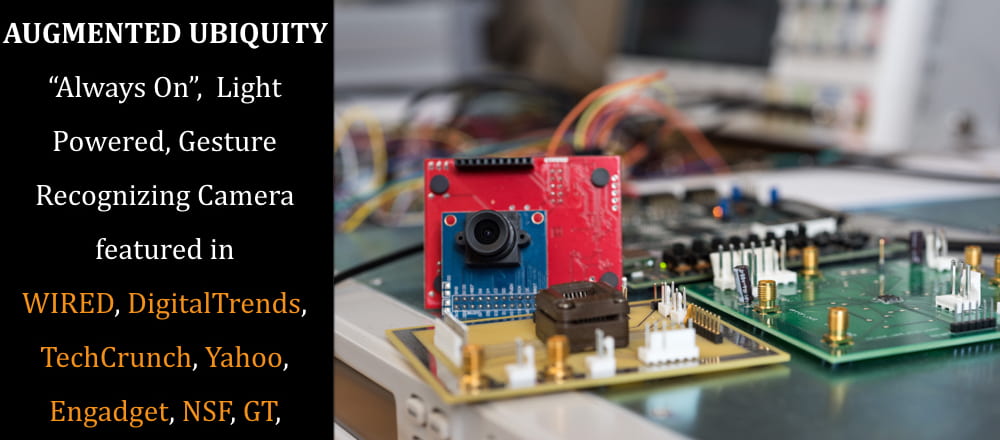

We explore mixed-signal hardware that can enable the next generation of autonomy in intelligent systems. We have pioneered computational data-converters that can perform in-situ classification on voltage as well as time-based ADCs. Our current work encompasses hardware solutions for voltage and process scalability, memory-centric processing and low-cost interconnect technologies for supervised, unsupervised and reinforcement based learning. We collaborate with device and technology researchers to understand how post-CMOS devices can enable next-generation of autonomous and intelligent systems. We have demonstrated world’s first hardware for reinforcement learning at sub-1mW targeted for autonomous robots. Our work on “always-on” smart cameras has been widely covered by media outlets including Wired, Engadget and TechCrunch.

Key Publications: [JSSC 2021][ISSCC 2020][ISSCC 2019][JSSC 2019][ISSCC 2018][VLSI 2017][ASSCC 2017][BioCAS 2017][TCAS-1 2017][TCAS-II 2016][IEDM 2014]

Evaluation of security vulnerabilities of hardware and software implementations of Cryptographic schemes

Implementations of mathematically secure cryptographic schemes may leak information about their secret keys through power consumption and/or EM radiations, which can be exploited by an adversary with physical access to the target device using statistical methods involving correlation analysis, or more advanced profiling techniques based on template analysis or machine learning. My primary research goal is to evaluate such implementations to identify vulnerabilities, and design countermeasures. More recently, I have been working on enabling privacy preserving computation by designing hardware accelerators for Fully Homomorphic Encryption and Post Quantum Cryptographic protocols, while assessing their side-channel leakages.

Key Publications: [ACM JETC 2021][ISSCC 2020][CICC 2020][DAC 2019][TVLSI 2019]

Cryogenic CMOS VLSI circuits for High Performance Computing

With the device and system performance scaling saturating, we need alternative technologies to bridge the gap until futuristic technologies become commercially viable. Cryocooling of systems provides performance benefits which can be amplified with the aid of technology co-optimization. My research goal is to accurately model the device behavior at low temperatures, analyze circuits and designs with the developed models and build/test circuits and systems capable of operating at low temperatures to demonstrate High Performance Computing.

Key Publications: [CICC 2021][EDL 2021][IEDM 2021]

Design of Voltage Regulators, Adaptive Clocking, and Power Management

This project explores the design of on-die power management circuits with novel voltage-regulator architectures that are suited for digital logic. The focus of the work is to develop control architectures and corresponding hardware implementations that provide stability and performance across wide dynamic ranges of operation. Our principle interests are in linear and switched capacitor regulator topologies that are compact, low overhead and highly efficient.

Key Publications: [JSSC 2018][ESSCIRC 2016][ESSCIRC 2016][ISSCC 2015][JSSC 2014][Symp. on VLSI Circuits 2012]

Computation with Non-linear Dynamical Systems

While Boolean, Von-Neumann machines have fueled the technology revolution over the last three decades, it is well recognized that brain-inspired computational models are well suited for tasks such as data classification and recognition. Our current work is at the interface of non-linear dynamics exhibited by correlated electron devices and the computational models that are made possible by such complex systems. We are engaged in active research in the “information processing” capabilities of non-linear dynamical systems where the dynamics of synchronous oscillators are stimulated, controlled and observed; and can be shown to perform tasks such as associative matching. Our work on non-linear dynamical systems that connect dynamics with algebraic graph theory has been widely covered by media outlets including Phys.Org, Engadget and TechCrunch.

Key Publications: [Nature SR 2017][Journal of Applied Physics 2015][IEDM 2014][Nature 2017] [JETCAS 2014][DAC 2014]

Energy vs Accuracy: Computational Models and Hardware for Sensors, Sensor Interfaces and Signal Processing

Designing CMOS based sensors, sensor interfaces and low-power processing of sensor data is of interest not only for environmental sensing but also for advanced human-machine interfaces. We are interested in the design and applications of on-chip sensors like temperature, voltage, and current sensors as well as in building platform sensors (audio and video) that will enable seamless interaction of human and machines. Currently, we are exploring novel hardware concepts in compressive sensing, random sampling and processing in reduced dimensions with a focus towards approximate computation. This includes understanding and exploring mathematical models as well as physical realization of such models in digital and mixed signal domains.

Key Publications: [ISSCC 2009] [JSSC 2009] [CICC 2012]

Spintronics: Beyond Charge Based Computation and Storage

Prof. Raychowdhury is an expert on device modeling, compact modeling, circuit design, and test architectures for Spin-Transfer-Torque based Magnetic RAMs (STT-MRAMs). Our research group is exploring improved device models for fast evaluation of process parameter variation in STT-MRAM with a focus towards different failure models. Current work includes identifying circuit architectures and test generation methods for designing and characterizing robust STT-RAM arrays in embedded designs. More recently, we have been exploring the application of Spintronic devices in analog and mixed signal computation.

Key Publications: [IEDM 2009] [IEDM 2010] [IEDM 2011] [TED 2011]

Design of Low-Power Digital and Mixed-Signal Circuits with Emphasis on Adaptability and Resiliency

We are interested in exploiting the limits of low energy design with adaptation and resiliency against dynamic variations and errors. The aim is to minimize design guard-bands to ensure error free operation with a need for error detection and correction in case of rare failure events. We study circuits and architecture for both logic and embedded memory.

Key Publications: [JSSC 2011] [ISSCC 2011] [Symp. on VLSI Circuits 2010]